Other Parts Discussed in Thread: ADS1282

Dear Christopher,

in order to keep the reference voltage as stable and clean as possible, I connected the AVDD pins to a dedicated 5V_SENS power supply sourced by a linear voltage regulator and kept the VREFP pin connected to a reference 5V generated by an AD584 reference generator with an external NPN transistor.

It happened that my 5V_SENSOR power supply was switched off because of a supposed failure, while VREFP stayed switched on.

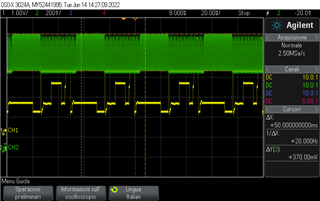

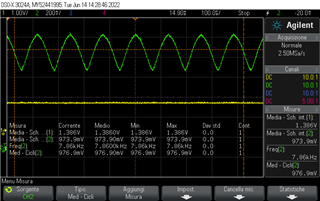

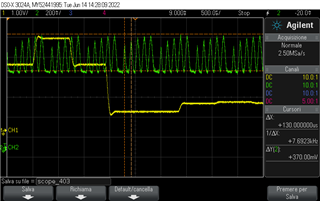

The ADC started sinking 40mA on the AVDD and providing acquisitions with doubled value as it was selected PG = 2. All commands were perfectly interpreted and implemented by the ADC and, by the way, I continuously write CONFIG1 register to keep PG = 1 selected. Furthermore, I checked the output of the PGA and it was giving evidence of a 1x gain selection.

I deemed the ADC as damaged and removed it from the PCB.

My question is:

Could the presence of VREFP while AVDD was absent be the root cause of ADC failure?

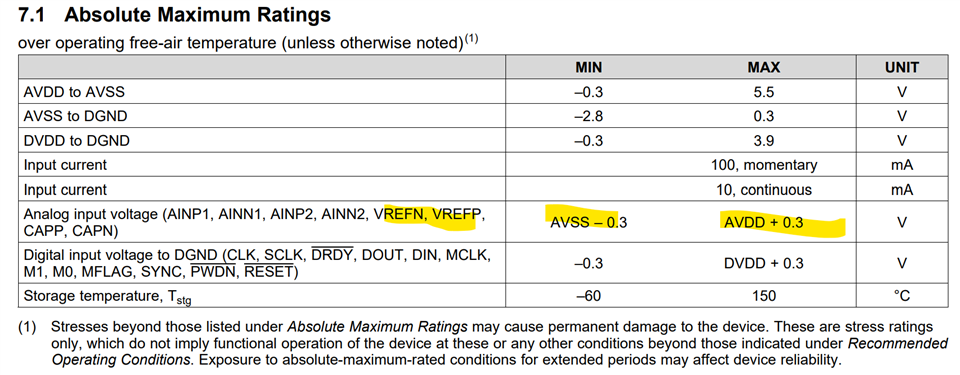

Additional information: the ADC, because of the absence of many sensors, resulted also fed by a 12V input for about 16ms in a 50ms period (1/3rd of the period) absorbing about 11,5mA on AINP pin - (12V-0.6V)/1kohm -, which is more than the 10mA continuous input current limit but much less than the temporary 100mA input current limit.

Thanking you in advance,

Best regards,

Daniele Lippi