Hello All,

(1) ADC suggestion - Data converters forum - Data converters - TI E2E support forums

Continue to this post....

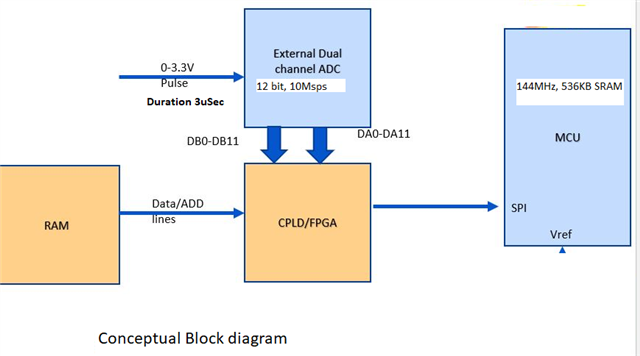

need to capture continuously, 3us pulse appearing periodically coming from 2 identical channel. we are expecting more samples so planning to go with 12bit 10Msps ADC, we are looking for suitable dual/ 2-single channel ADC.. because of high speed we need process more data. for that attached block diagram circuit fallowing. pls suggest suitable ADC and review connection to MCU. (MCU is fixed)