Hello,

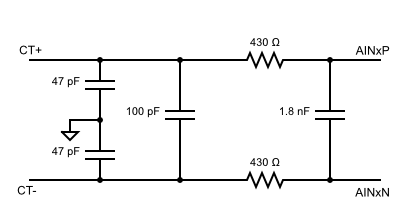

The company I am working for is using the ADC ADS131M06 for sampling the output of a current transformer (CT) that has an integrated burden resistor, therefore outputting a voltage of 0.333V over relatively long twisted wires of around 1m. When the CT is used in a noisy industrial environment, the output of the ADC is corrupted by environmental RF noise, most probably due to motor drivers (VFDs) located nearby. Other channels used for sampling the high-voltage (with a resistive divider) are not affected by this noise, indicating the noise is likely coming from the CT cables and not from the PCB itself. The signal of interest is located between 1Hz and 10kHz, the noise is in the range of 20-100kHz. The electrical design that is used today between the CT cables and the ADC can be found in attachment.

- Can something be done on this circuit to improve the noise immunity?

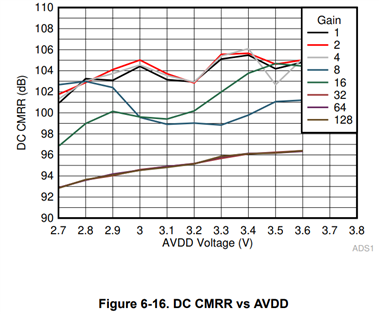

- For now, we use the PGA with a unity gain, while we could go to a gain of 2, maybe 4. Would increasing this gain be beneficial in our situation? My guess is it will also amplify the noise...

Thank you very much in advance.

Best regards,

Nicolas Verbeek