Other Parts Discussed in Thread: ADS54J64EVM, ADS54J64, LMK04828

I have started modifying the zc706_8b10b reference design so that I can directly connect a ADS54J64EVM to the ZC706 but I have run into a few issues. I plan to use the ADS54J64 is mode 0 (LMFS = 4841) and set the sampling rate to 280MSPS, which makes the output of the ADC 70MSPS due to the 4x decimation.

My questions/issues are:

1. The sysref and clkin pins of the ADS54J64 on the ADS54J64EVM is connected to pins on the FMC that are no connects on the ZC706 board. Does this mean that the only way to provide these clocks to the ADS54J64 in this setup it to use the “ADS58J64EVM GUI” to configure the LMK04828 on the EVM board to provide 280MHz sampling clock? Do I need to do this everytime I turn on the boards? Are there instructions to be able to set the proper settings in the GUI because the ADS54J64EVM Manual.pdf does not explain this.

2. This and question 3 kind of go together. I am a little lost at exactly what the MGT REF CLK should be. Should this be at the sampling frequency or the ADC output rate? Should this be coming from the LMK04828 (FPGA_JESD_CLK or FPGA_JESD_Sysref) depending on what your answer is to my question 1? The user guide for this core just says “These must be connected to the MGTREFCLK pins of the FPGA”. The FPGA_JESD_CLK signal from the LM04828 on the ADS54J64EVM is connected to the FPGA’s MGTREFCLK0 pin through the FMC. Is that what this means?

3. What exactly should my line rate be set at. I found this equation, where M=# of converters, S=# of transmitted samples per converter per frame, N’= JESD204B word size, FC=frame clock, and L=number of lanes.

Lane Rate = (MxSxN'x10/8xFC)/L

For my application, M=8m S=1, N’=16, L=4 I believe. I think my frame clock is 70Mhz since I want to sample at 280MSPS and mode 0 has 4x decimation. Is this correct? If so, my lane rate should be 2.8GSPS

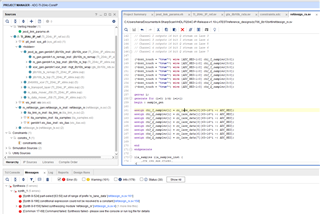

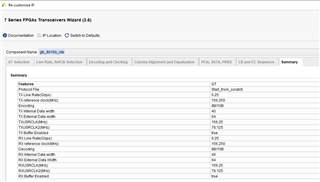

4. I have attached my modified jesd_link_params.vh, gtx_8b10b_rxtx.sv, and constraints.xdc files for reference. The only modification I made in the “7-series FPGAs Transceivers Wizard” for gtx_8b10b_rxtx is that I turned TX off in the “Line Rate, RefClk Selection” tab. I attached pictures of the summary from the wizard for reference. With these modifications, when I try to synthesize, I get an error, which I also attached as a picture. I am not really sure why. I initially changed the NUM_RX_LANES to 4 within the refdesign_rx.sv file since that’s how many output lanes the ADC has. I changed it back to 8 and reran synthesis but get the same error. According to the ADS54J64 datasheet, the IQ data are on the same lane for each channel. My intention is to modify the reference design and the package the entire thing as IP to be used inside a larger project. Should I need be trying to package the entire reference design?