Other Parts Discussed in Thread: OPA350, TPS7A47, ADS1261, ADS131E08

Hi,

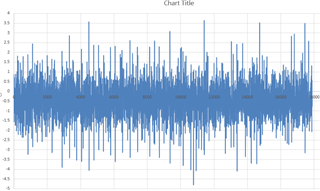

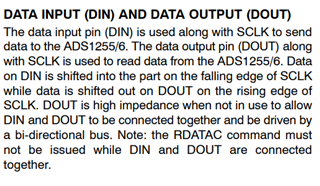

I am working on ADS1256 using Verilog code. I am reading the converted data in continuous mode. Current setup is with three differential channels connected and remaining kept open. The issue is I am finding noise glitches on the output with and without load on all the three channels. I tried even with shorting the inputs (ie 0V) for one of the differential channels. The issue is unchanged. Is that a common fact in this ADC? The sequence of operation I followed is: SELFCAL (after power-up), SDATAC, STATUS, ADCON, DRATE, IO_REG, SELFCAL, MUX, RDATAC (with loopback). The DREADY is as per the DRATE I had set. I even made sure that no glitches on SCLK. The master clock is at 7.68 MHz and SCLK is at ~1MHz. One of the images I had attached for reference of one of the differential channels. It is at DRATE 3750 SPS with PGA 64.

And, I tried with data rates of 100, 500, 1000, 3750, 7000, 15000 SPS and with PGA 64, 32, 8. Issue is the same. Is there any limitation in the ADC? I want the design to work at PGA 64 and DRATE at 3750 SPS. The schematic requirements are made sure as per the datasheet. Could you help me in resolving this noise at the output?

Thanks