Hi,

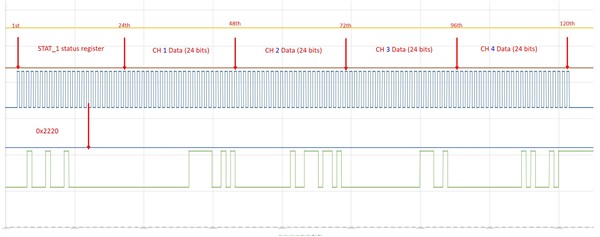

we use the ADS131A04 in our design and it work. But in every conversion result the status bits are 0x2220 ... Why ?

Here my initialisation : (M0 Vdd | M1 and M2 GND -> 24 Bits)

ADS131A04_Unlock() ADS131A04_Reset() ADS131A04_Unlock() ADS131A04_ReadReg(0x00) ADS131A04_WriteReg(0x0b, 0x78) ADS131A04_WriteReg(0x0c, 0x32) ADS131A04_WriteReg(0x0d, 0x02) ADS131A04_WriteReg(0x0e, 0x25) ADS131A04_WriteReg(0x11, 0x00) // ADC1 Gain 1 ADS131A04_WriteReg(0x12, 0x00) // ADC1 Gain 4 ADS131A04_WriteReg(0x13, 0x00) // ADC1 Gain 1 ADS131A04_WriteReg(0x14, 0x00) // ADC1 Gain 1 ADS131A04_WriteReg(0x0f, 0x0f) ADS131A04_Wakeup() ADS131A04_Lock()

All commands answer correctly.

When the ADS is start and I shift out the 15 bytes (1x Status + 4x ADC results ) the first two bytes are 0x22 0x20 . Why ?

The ADC results look okay.

Thank you for your help