- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

How is tDACWAIT defined? The datasheet only gives a duration (2.4 us). What event marks the beginning of the tDACWAIT interval, and what event must not happen until after tDACWAIT? Are these points different when using asynchronous updates versus synchronous updates?

Hi,

tdacwait is the digital delay between transactions to free up the bus internally to the device.

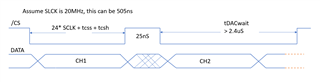

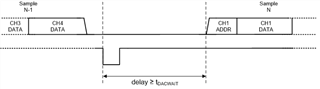

It is defined as the time interval between subsequent LDAC falling edges in synchronous mode or the interval between subsequent CS rising edges in asynchronous mode. Basically, the way tdacwait must be interpreted is as the delay between the latch edge and the CS falling edge of the next DAC command.

During the tdacwait time, data register update is blocked.

for example, if we need to update Ch1 data, sequence should be as follows. Applicable for multichannel update using LDAC as well.

Ch1 -- > Tdacwait ----> Ch1

Hope this clarifies your query.

Regards,

AK

Does this mean that tDACWAIT doesn't overlap for each channel in asynchronous mode? I would expect tDACWAIT to apply on a per-channel basis, so that this would be legal:

Ch. A -> tDACWAIT -> Ch. A

Ch. B -> tDACWAIT -> Ch. B

Ch. C -> tDACWAIT -> Ch. C

Ch. D -> tDACWAIT -> Ch. D

with this sequence iterating over a period that is less than 4 x tDACWAIT. For example, this sequence should be able to iterate at 192 KHz (5.2 us). It sounds like you are saying that tDACWAIT applies between any two updates, even to different channels.

Hi,

In asynchronous mode, since /LDAC is not involved, we can define tdacwait as interval between subsequent CS rising edges . When Ch1 is updating, you can write into Ch2 by pulling /CS low, but the frame length should be min 2.4uS. This is because we have shared resources across channels.

So I would say best approach is as follows.

So tdacwait is not per channel basis. If you want the best throughput from device, use synchronous mode and write into all registers and trigger using /LDAC.

OK. So in synchronous update mode is tDACWAIT the interval between falling edges of /LDAC, or is it from the falling edge of /LDAC to the next falling edge of /SYNC? You sent me this diagram:

That looks like falling edge of /LDAC to falling edge of /SYNC.

Hi,

/LDAC going low to /CS going low can be taken for synchronous mode.

Regards,

AK