Other Parts Discussed in Thread: LMH5401EVM, LMH3401EVM, LMH3401, LMK04828, LMX2582

Hi everyone,

we have an issue with adc samples reaching a stable baseline after changing dc input level.

Following a detailed description:

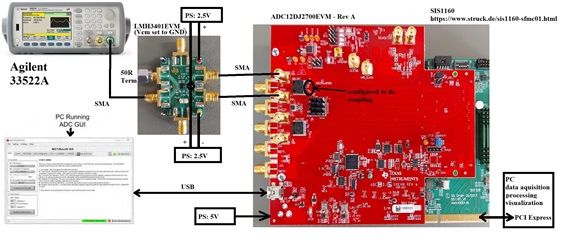

Hardware:

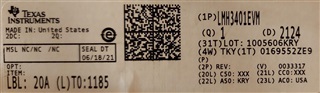

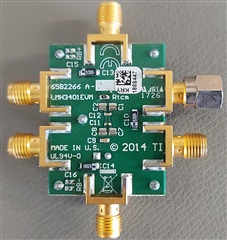

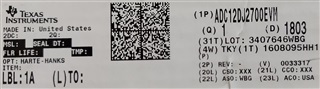

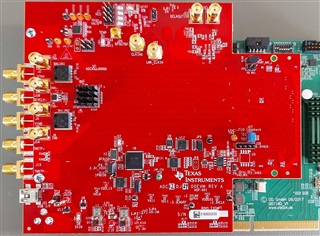

- Evalboard ADC12DJ2700EVM

- Evalboard LMH5401EVM (CM input connected to GND)

- AWG square wave 50 second high, 50 second low (level like to see in sample data)

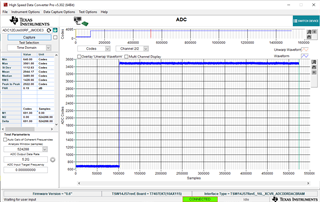

Setup with "ADC12DJxx00 GUI":

- Evalboard LMH5401EVM SMA IN+ driven from AWG square waveform (dc coupled), SMA IN- terminated 50 Ohm

- LMH5401EVM SMA Out +- connected to ADC12DJ2700EVM SMA INA+- (Channel A dc coupled)

- ADC clock 2.5 GHz (onboard generated)

- ADC analog input range default

- JMode 0 (single channel 5GSPS)

- ADC data format offset binary (data decimal 2048 correspond to differential input level 0V)

- One time ADC setup and started, continously free running sampling

- taking samples from adc data stream after certain delay

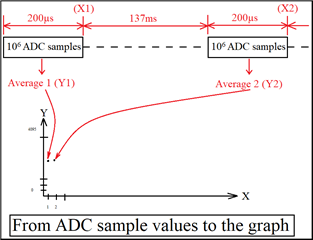

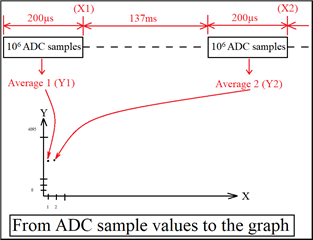

Data processing:

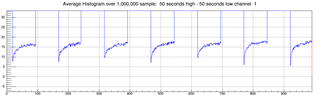

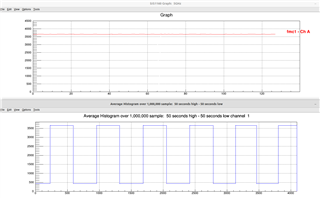

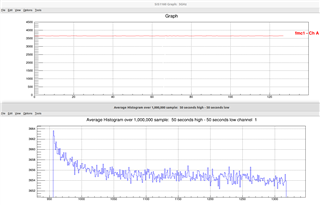

- each point along x-axis in diagram correspond to an average over 1 million samples (0.2ms trace)

- every 137ms one data point

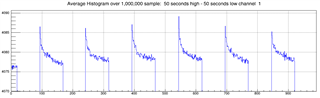

- AWG level adjusted to ADC data about decimal 3655 (high level) and 445 (low level)

- see picture screen4.png

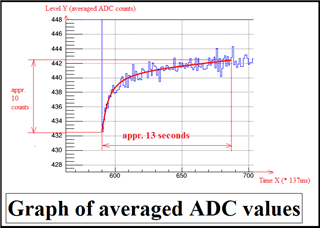

What we can observe:

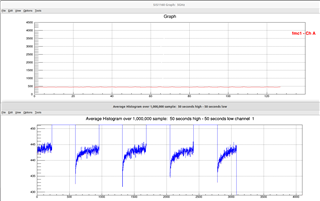

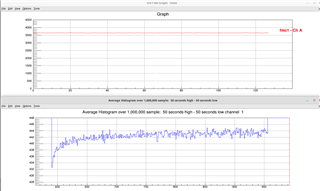

- at the signal edge (rising or falling), the "Average data point" shows an overshoot

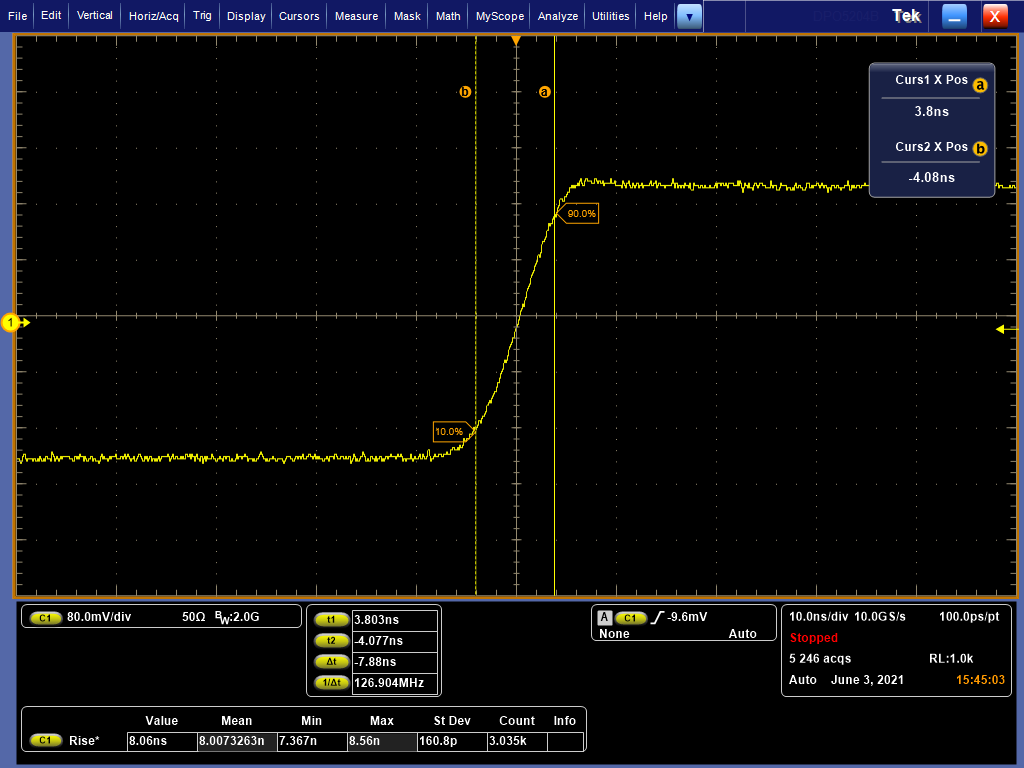

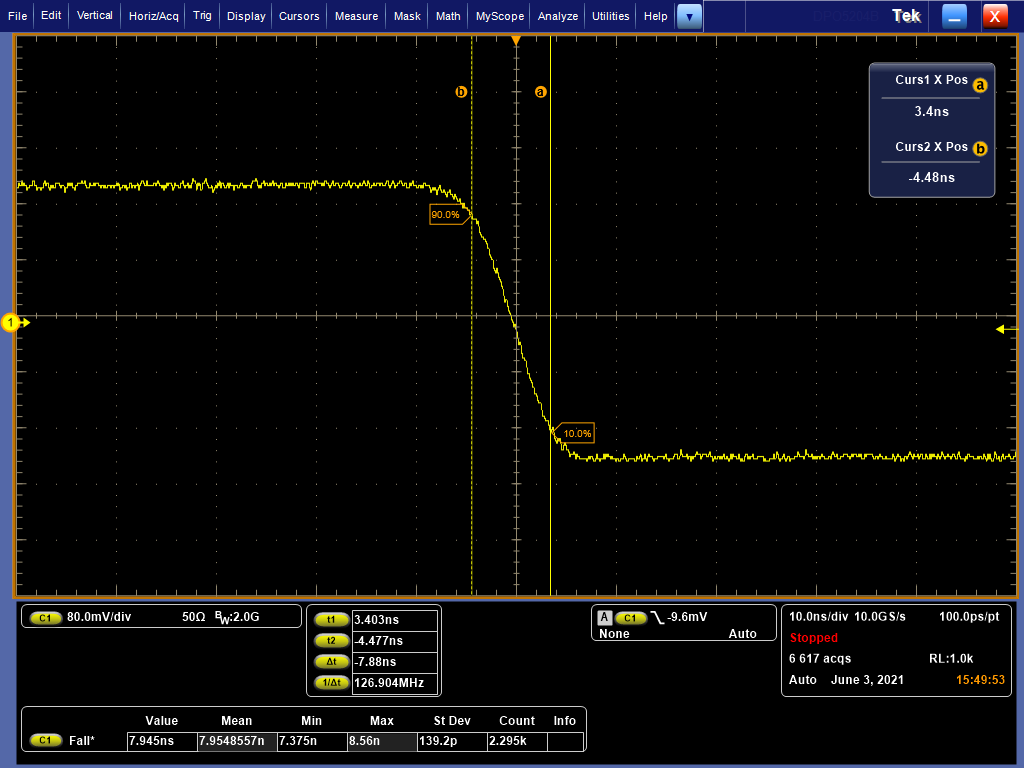

- see picture screen2.png and screen3.png

- like an capacitor charge or discharge curve, the "Average data point" needs some time (~1 Minute?) to reach a stable value (baseline value)

- zoomed in of overshoot region, see picture screen5.png and screen6.png

Can you confirm this behavior?

Can this be improved or avoided?

Best regards

Andreas