Part Number: DAC37J84EVM

Hi everyone,

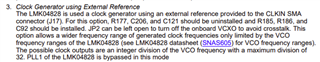

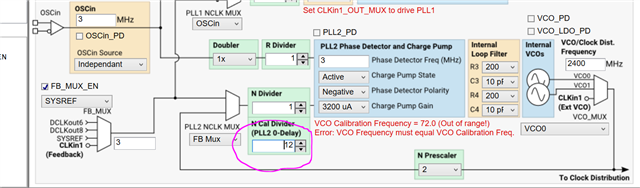

I use DAC37J84EVM board with external reference to OSCin. I did modification that is mentioned in user's guide (attached picture).

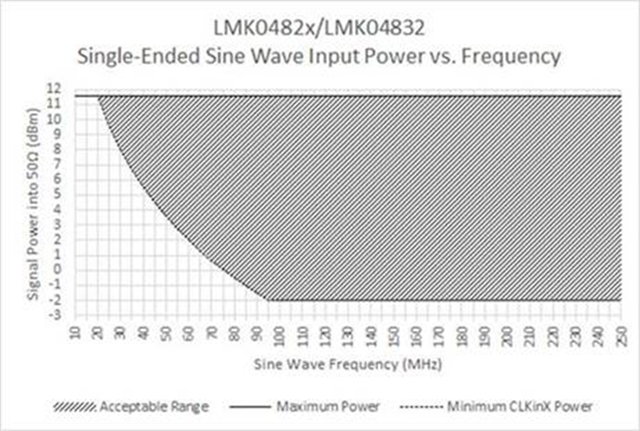

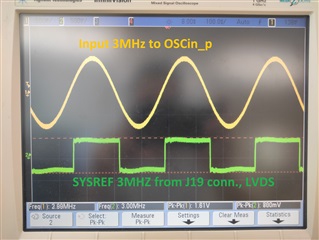

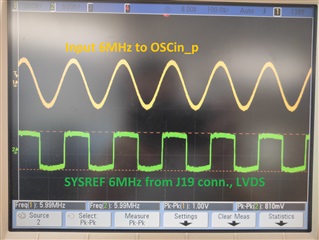

I'm using an external reference 3 MHz 2 Vpp.

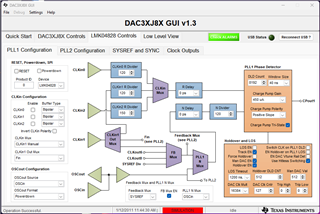

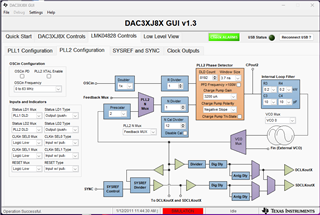

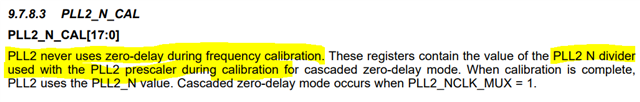

PLL2-only zero-delay with SYSREF feedback through Feedback Mux.

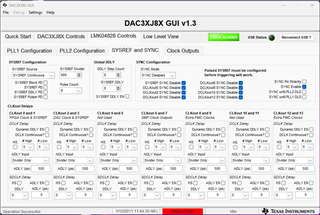

SYSREF divider = 800. Expected VCO0 frequency = 3 MHz * 800 = 2400 MHz.

When I load the configuration, usually the PLL2 doesn't lock. It locks only when I change SYSREF divider to 920 (sometimes to 812), but the VCO0 frequency becomes higher (3 MHz * 920 = 2760 MHz) than the maximum mentioned in datasheet (2630 MHz).

Why doesn't it lock with SYSREF divider = 800?

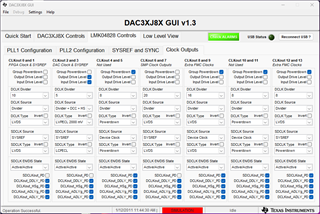

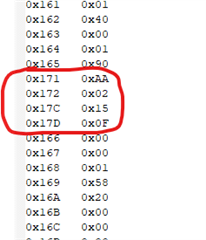

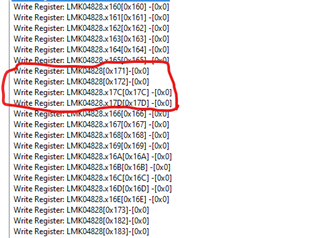

Attaching my config from DAC3XJ8X GUI.