I had an issue reading the device ID a while ago, and was able to fix the issue by simply switching from nRF52840 to an STM32. However, I still want to figure out why SPI communication did not work with the nRF52840, despite sending the exact same command, and AFAIK obeying all of the timing requirements.

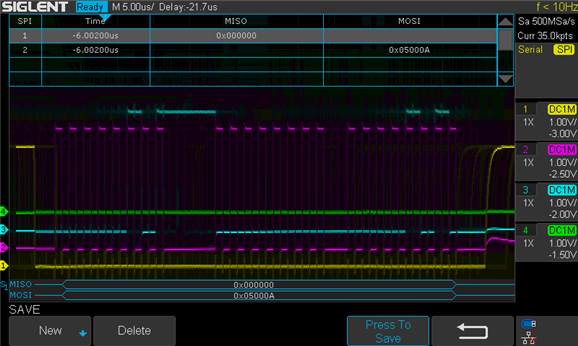

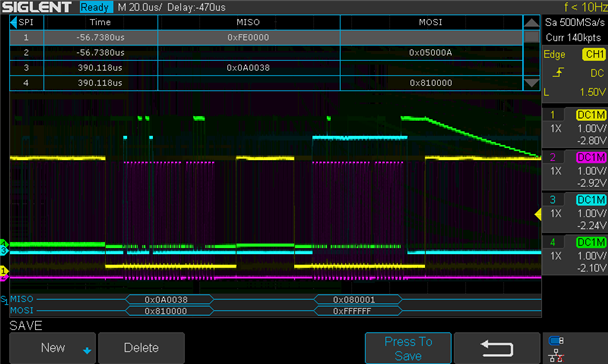

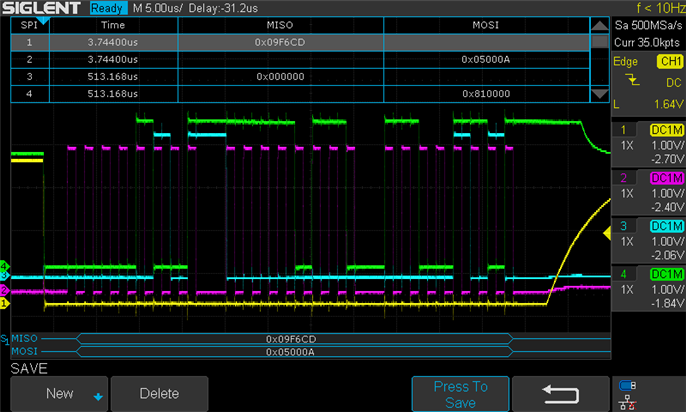

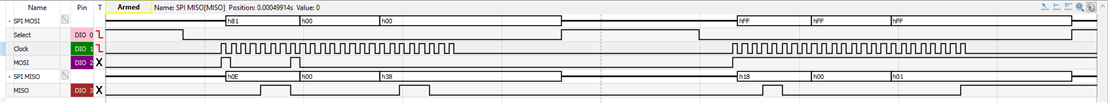

This first capture is from the STM32, getting a proper address echo and Device ID read back.

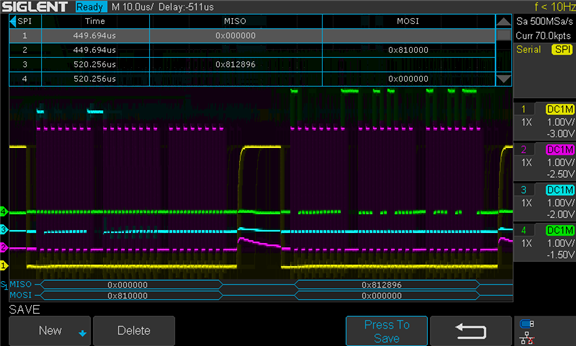

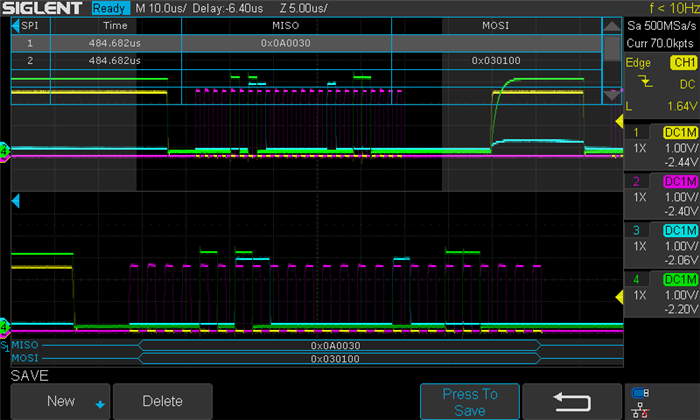

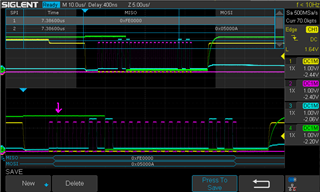

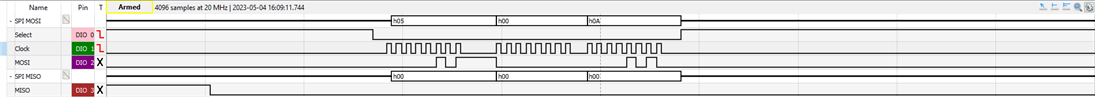

This second capture is from the nRF52840, with the exact same Read request sent. The DAC fails to echo or read back the Device ID in the subsequent access cycle.

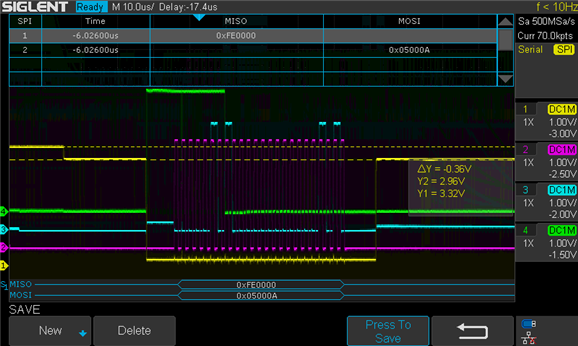

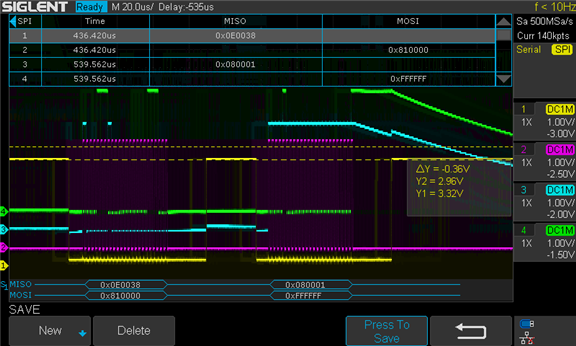

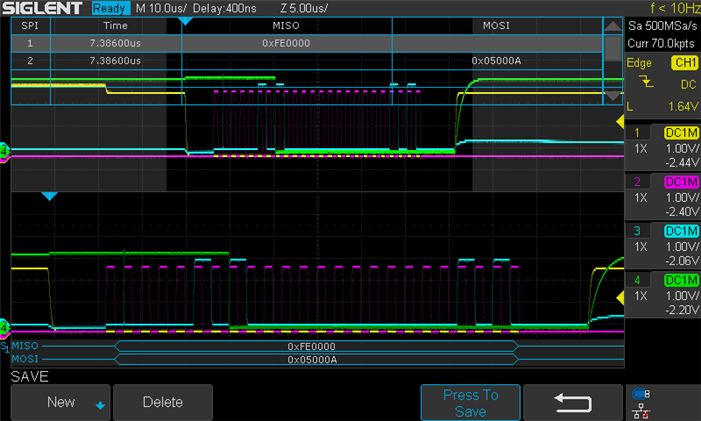

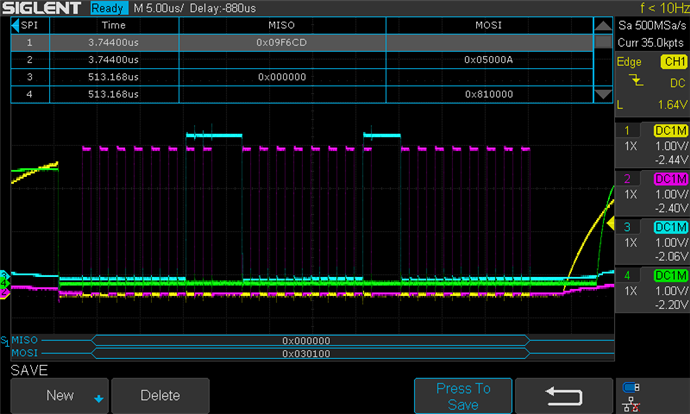

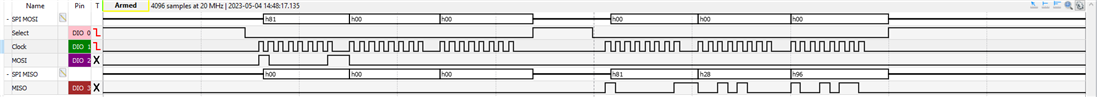

In both cases, the chip is soft reset prior to the Device ID read attempt, as follows:

Any assistance would be greatly appreciated, thank you!