Other Parts Discussed in Thread: ADS1299

Hi everyone,

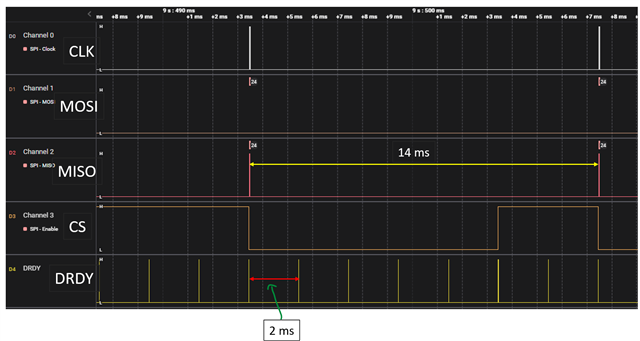

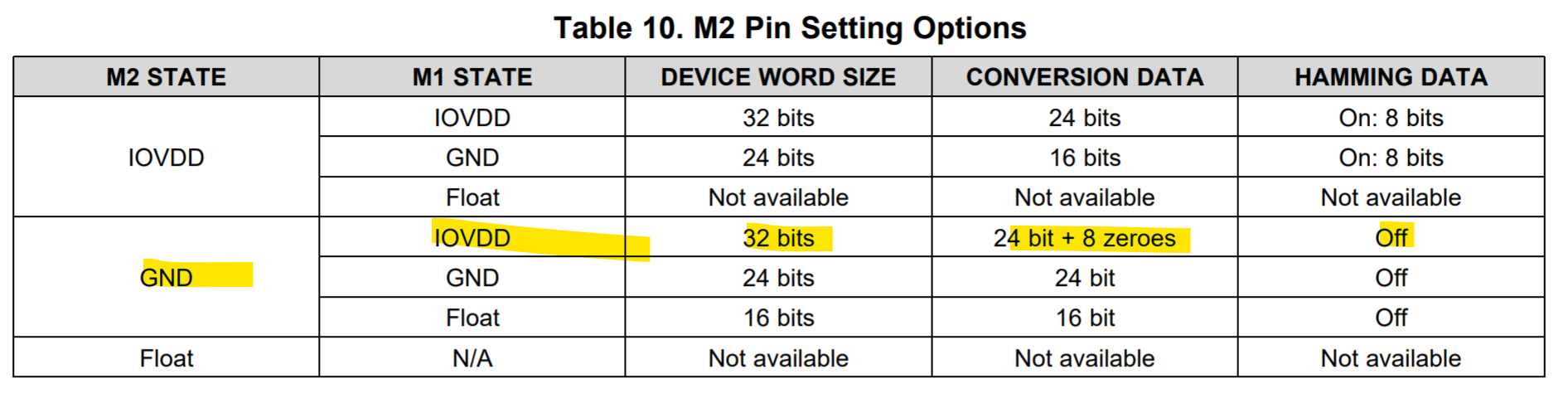

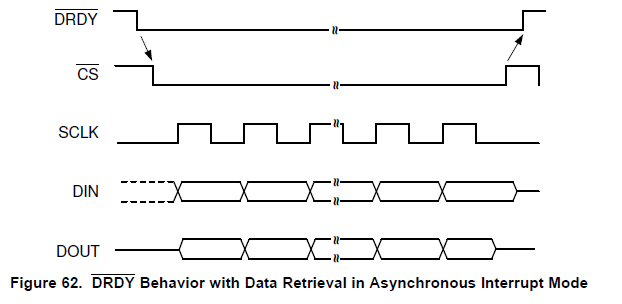

I'm trying to connect ADS131A04 Eval board with nRF52 Dev KIT. I was able to write & read all registers correctly. I'm following the instruction shared in other post to initialize and read the ADC data. I'm using Asynchronous Interrupt Mode with fixed data frame to read out the data. The following is what is supposed to see if I successfully did with this mode. The DRDY goes low when having data from DOUT (MISO).

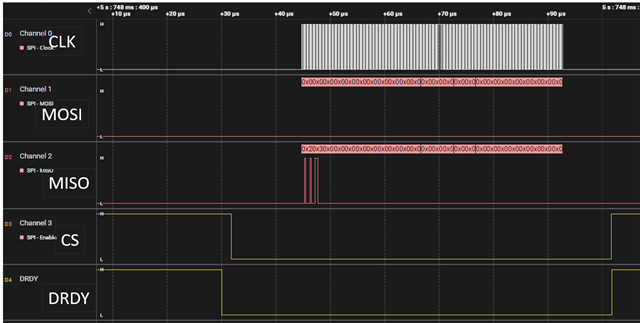

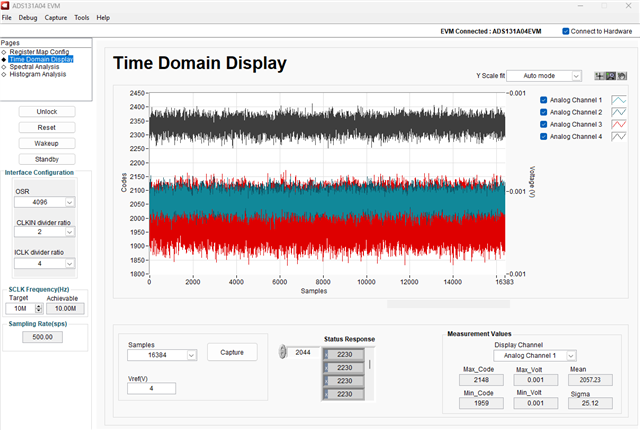

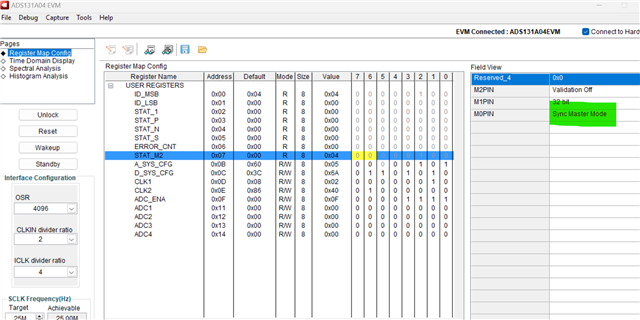

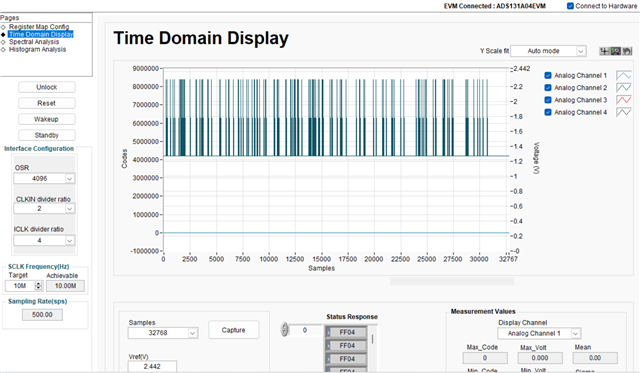

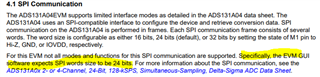

However, in my case I read data from STAT_S (SPI status register) and it showed 1 in its bit 0 - meaning that it was not enough SCLKs are sent per frame. It reflected in the following image. I'm using 4MHz for SPI's SCLK which worked well before with different ADS chip (ADS1299). Thus, I'm wondering if I set up anything wrong. My expectation is that whenever DRDY is low (every 2ms as I setup with CLK2 register), I would see data coming out from MISO pin, however, there was only 2 data sequences came out after 8 times of the DRDY goes low.

Hope to receive any suggestions from TI support team and other forum members! Thanks Tai.