Other Parts Discussed in Thread: DAC3152, , TRF370417, DAC3174, TRF3705

Unfortunately I couldn't find any schematics from DAC31x1 nor DAC31x4 (these would be pin compatible). Also the EVM board doesn't have any schematic with it. I would appreciate it, if you would send me these along with the layout of your design, so I can orient myself on the the constraints. The datasheets are missing some informations, that I would like to clarify here:

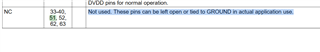

1. The DACCLK is LVPECL (for that the Common-mode voltage is 2V, but in the datasheet it's mentioned as 0.5V?), but in another datasheet (DAC3152 page 17/32) you mentioned that the DACCLK pins are internally biased and "Although not optimal due to the limited signal swing, an LVDS source can also be used to drive the clock input", but I'm not sure, if this applies to the DAC3154? The LVDS has VDIFF of 400mV, so it's barely the minimum of what DACCLK could take. Is this a reliable clock configuration? Only AC coupling won't do much, but your internal biasing is maybe helpful?

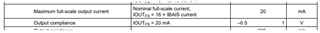

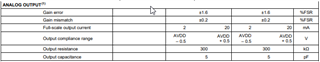

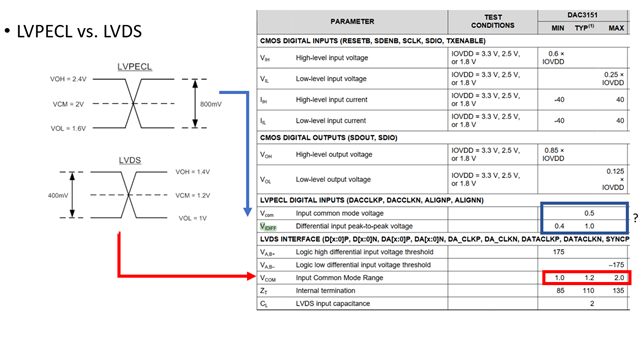

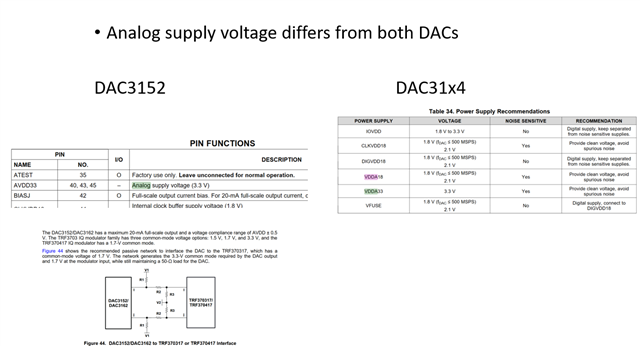

2. I want to use (just as in DAC3152 mentioned) the modulator TRF370417, then I have to match both common-modes (DAC output common-mode is AVDD +/- 0.5V) and from modulator 1.7V. For the DAC3154 we have two different Analog supply voltages (AVDD18 and AVDD33), so which one should we take into considration for the output common-mode voltage (This was already discussed in this question: https://e2e.ti.com/support/data-converters-group/data-converters/f/data-converters-forum/462985/dac3152-output-level-low)

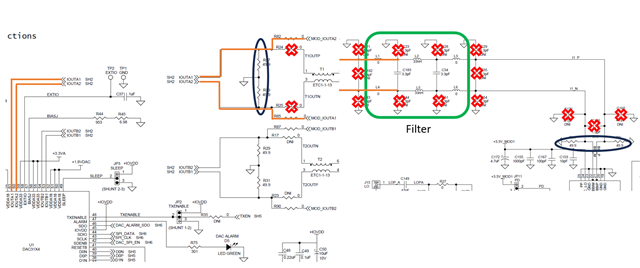

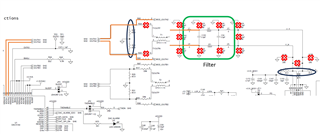

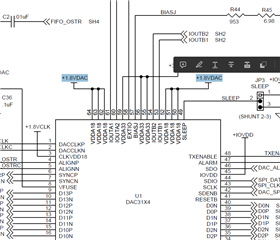

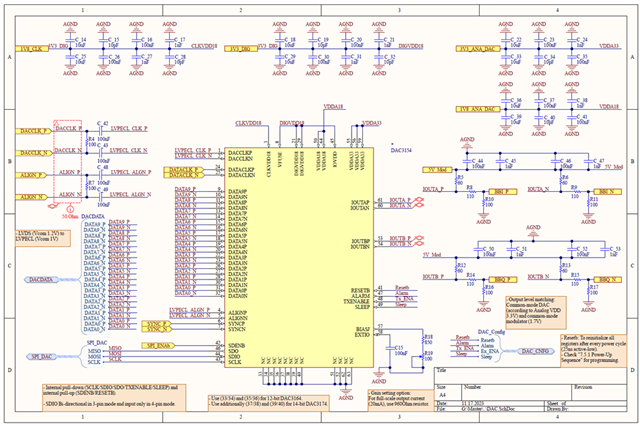

Here's my initial schamtic for the DAC3154, but I need still to figure out both these uncertainties:

Any help would be much appreciated!