Part Number: DAC37J82

Other Parts Discussed in Thread: LMK04828

Hi Ti

I have a question on the Common- and differential mode input level on the DAC37J82

The datasheet states

- Vcom = 0.5V

- Vidpp = 400 to 800 mVp2p

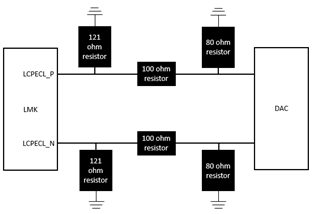

The DAC SYSREF termination on the EVM Board is

- 200 Ohm to ground

- 100 Ohm series + 100 Ohm parallel (voltage divider)

The IBIS model simulation of this setup provides a 200 mV Diff p2psignal with the P&N level at 850 & 1005 mV,

This violated both the Vcom and minimum input Diff voltage specification of the datasheet.

Questions

- What is the minimum Diif input voltage for SYSREF

- Is a Vcom of 1V +/- 200 mV acceptable

Should the DC coupled SYSREF termination be changed to more closely match the SYSREF specification in the datasheet?

Please advise

Thanks

Piet