Hi,

I would like to confirm the minimum required differential input voltage for the DAC38RF89 SYSREF and DACCLK inputs. The datasheet says typical 800mV and max 2000mV. I understand max is top value above which input differential voltage should not exceed, but what is the minimum required input differential voltage for these inputs to guarantee the DAC38RF89 sees valid input switching transitions?

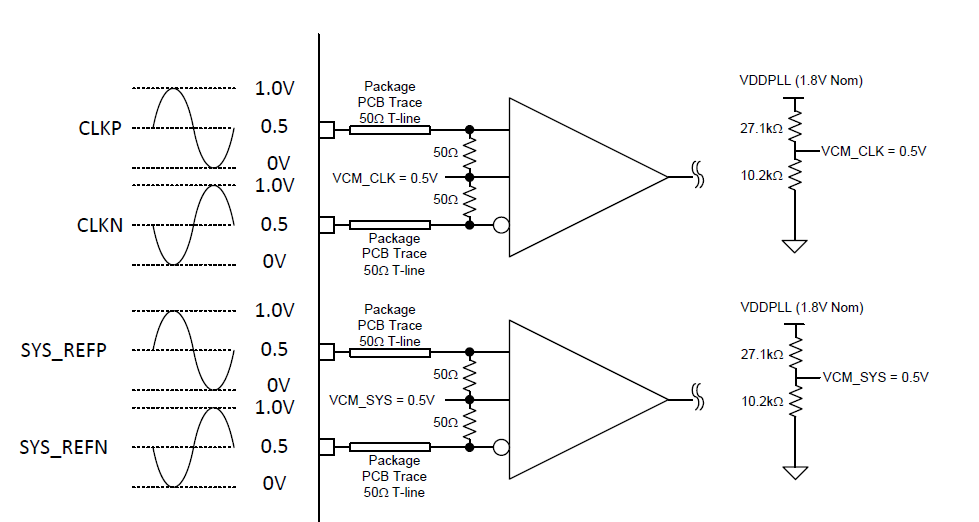

Also, the common mode voltage is listed as 0.5V typical. What is the min/max Common Mode voltage the CLOCK/SYSREF driving circuit must meet? For the clock can AC couple, but SYSREF cannot be directly AC coupled as it has significant DC content.

Thanks!