Dear Expert

Due to the inconsistency between the configuration frequency and output data rate of the ADC chip ADS1220IPW in the pressure detection board, the board cannot be used normally.

Exception description:

The DR bit of software configuration register 1 is configured to be 110 in normal mode, with a theoretical data rate of 1000sps according to the specifications, using continuous conversion mode. Batch chip output abnormality occurred, range: 970-1301sps; Abnormal materials account for 10%.

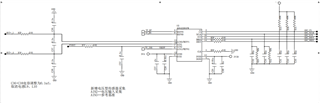

The schematic diagram of ADS1220 is:

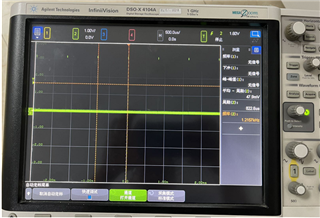

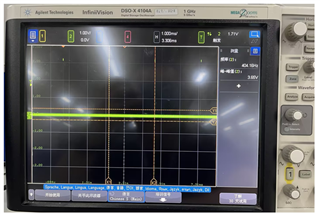

Abnormal board, DRDY outputs frequency waveforms in 1000sps and 330sps configurations respectively:

Troubleshooting points:

1) Remove the resistance of CLK pulled down to ground, 0R, and maintain the abnormal frequency;

2) Remove the series resistance, pull-up resistance, and filtering capacitor related to DRDY, keeping the abnormal frequency unchanged;

3) Heating up ADS1220 results in a change in DRDY frequency and an increase in frequency.