- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

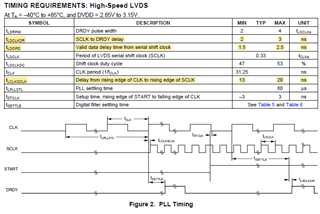

I am working on a design with 16 x ADS1675 operating in synchronization. What is the CLK to SCLK delay , TLCLKSCLK, when all ADCs are running on the same voltage, 3.0V +/-1%, and all are operrating at the same temperature, between 40C and 70C for example. Attached is the relevant figure 2 timing diagram from the data sheet; note the data sheet gives the delay over voltage and temperature as well as process. Here, I am asking what variation I can expect in the PLL timing due to process alone.

Hi Robert Wood,

Please note that our support is limited during the holidays, expect a response during the week of January 2

-Bryan

Hello Robert,

I discussed your request with the design team, and unfortunately, there is not an easy way to provide additional data on timing specs based only on process variation. Even if we were able to provide an approximation, you would not want to use these numbers in your design, as you could have problems in the field if the tightened specs were inaccurate.

Regards,

Keith Nicholas

Precision ADC Applications