Hi, Support

Currently we have a FPGA circuit board interfacing with DAC37j84 boards via FMC connector. However the power for FPGA board and power for DAC circuit board side are separated.

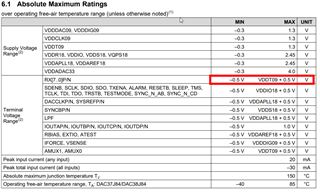

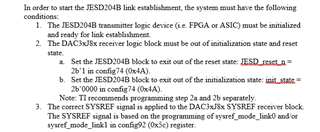

My question is that : " Is it safe the FPGA side powered up while the DAC side doing power cycling?? Will possible the Tx line from FPGA side causing any damage to the DAC end?? "

thanks

Li