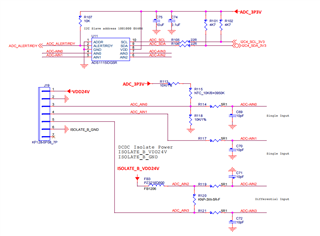

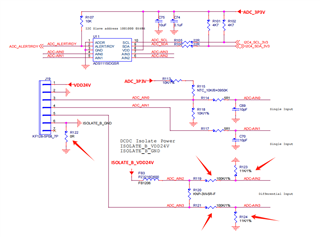

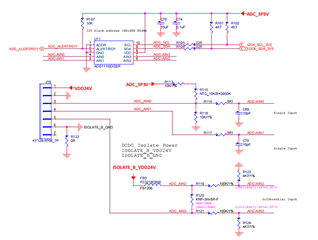

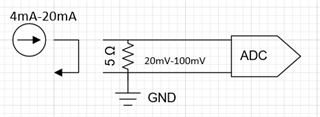

1.Our company's products use ADS1115IDGSR as the ADC function. The product is installed on a liquid transport car, and the J19 connector is connected to the liquid level transmitter.

2.AIN0/AIN1 software is configured as a single -end signal input, AIN2+AIN3 software configuration to differential signal input

3.After the product passes through the aging test, it is installed on the car, and the ADS1115IDGSR function appears abnormal;

4.Products with abnormal function, measure the pins of the ADS1115IDGSR chip, most of them are AIN1/AIN2/AIN3 impedance, and there are short circuits and roads.

5.What is the reason that causes ADS1115IDGSR abnormality? Is there a problem with the hardware design or the software configuration? Annexed ADS1115IDGSR principle diagram, please review and check.

Thanks!