Hello,

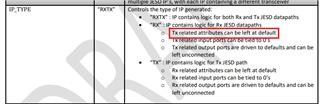

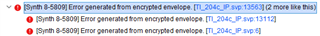

We are creating a FW project for our new ADC/DAC board that utilizes the ADS54J60 ADC and the DAC39J84 DAC. We are using the "TI204C-IP-Release-v1.12-LATEST" IP that in the README states that it works for 2022.x and above. However when synthesizing the IP core we run into problems with the following:

What exactly is happening on strings 13563, 13112, and 6 inside the encrypted sources?