Part Number: ADS1220

Tool/software:

Hello,

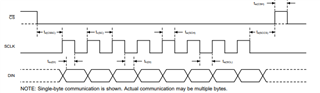

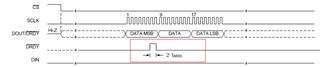

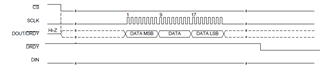

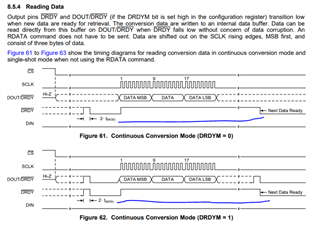

I'm using ADC in continuous conversion mode. In my application, the period of reading data operation is much longer than the period of ADC data update. For that reason on the logic analyzer, I'm able to observe short periodic high states of the nDRDY line between readings which might interfere with data reading. From my understanding, it will work following way in both ways of data reading:

- When triggering read with RDATA command it doesn't matter if the read is triggered on nDRDY state low/high/toggle. It always returns correct and consistent data. When reading takes place during periodic data update nDRDY state indicates if ADC provides old or new data.

- For the SCLK mode only information in the datasheet that I found is that the reading shall be synchronized with the falling edge of nDRDY line. But there is no information about the side effects of reading in different states.

So my questions are about the potential side effects of both ways of reading:

1. What will happen when reading data using the first SCLK rising edge when nDRDY high state?

2. What will happen when a data update (nDRDY pulse) takes place during SCLK rising edge data reading?

3. What will happen when reading data twice in a row using SCLK rising edge method? (Second read in state high)

4. Are there any other side effects of both reading methods that I should be aware of?

Thank you for your help.

Regards,

Sebastian