Tool/software:

Hi

What is the DRV function of LM51772? Will not using it affect the OCP function?

Thanks

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Stefan

Could you help the check below LM51772 schematic and any need to adjust

LM51772 Buck-Boost Quickstart Tool V1_1_1_20W.xlsmLM51772 Buck-Boost Quickstart Tool V1_1_1_65W.xlsm

Hi Gareth,

Please see below my review list and bold marked line items which should be checked again

65W design:

Phase margin is low for 6V input.

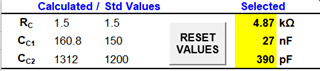

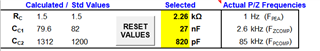

Better with

20W design:

Phase margin is low for 6V input.

Better with

Notes:

- it is not clear what should assembled and what not - e.g. check components on FB

- Device is LM51772RHAR (not PLM51772RHAR)

- could not track signals as search did not work in pdf of schematic

- adding a resistor divider on EN_UVLO between VIN and GND would allow to disable the LM51772 when input is low. To disable via Controller pull pin low via a Diode. Note: might need to be protected with a Zener for high input voltages.

- a newer version of the quickstart calculator has been published

For layout guidelines the layout please have a look at this application report first: https://www.ti.com/lit/pdf/slvafj3

Best regards,

Stefan

Hi Gareth,

the current limit can be set via I2C with this registers:

8.2 ILIM_THRESHOLD Register (Address = 0xA) [Reset = 0x64

But you also need to enable :

IMON_LIMITER_EN - should be set per default

and disable:

SEL_ISET_PIN in MFR_SPECIFIC_D9

Note: please ensure you have the right filter connected to ILIM for control of current limit via DAC

Best regards,

Stefan