Other Parts Discussed in Thread: ADS1285

Tool/software:

Hello,

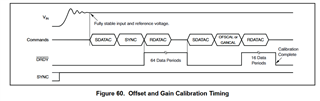

I have some questions about the calibration procedure shown below.

I want to further understand each command and their role.

1) Why is SDATAC first sent if it is followed later by a RDATAC? Is it because SDATAC must be sent before any other command (SYNC or R/W reg or others)?

2) Why is the SYNC signal needed?

3) I understand that the RDATAC and 64 data period is to allow proper settling of the FIR filter. Is that correct?

4) Why is SDATAC needed again? Is it because OFSCAL/GANCAL must be sent only when we are not in read continuous?

5) Do we need to do OFSCAL before GANCAL or is the order unimportant? I assume offset removal is important for the gain calculation, but I couldn't find confirmation for this.

I would have expected this simpler sequence to work:

1) Wait for settling of reference voltage and input voltage

2) Send the OFSCAL/GANCAL command

3) Wait 16 drdy cycles

I have another question about SDATAC:

1) Is it necessary to go in SDATAC mode for any command, whether is it read or write? I expected it to be needed only for read command because of the sharing of the dout signal, but the further I read, the more I understand that any spi command needs to be done in SDATAC mode.

Thank you,

Vincent