Tool/software:

Hello,

I would like to configure Microchip's JESD204B core for PolarFire FPGA together with the ADC12QJ1600 ADC.

Hardware has all 8 lanes connected to the FPGA.

I would like to use JMODE9 (8-bit, 8B/10B encoding, 8 lanes), Basic question is

1. How should I configure the ADC ?

2. How should I configure the FPGA JESD core?

Following is the setup and configuration I am thinking of considering.

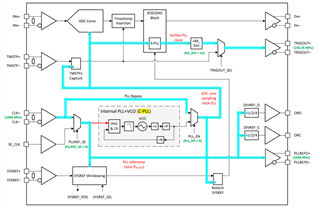

Clocking setup for ADC

Configuration Sequence for ADC:

As per the below datasheet

Pins: PLL_EN = '0'; PLLREF_SE = '0'; CLK+/- = 1000 MHz;

Step1. PD = '1' (For how long this should be high ? Right now ~40 us)

Step2. PD = '0' (For how long this should be low? Right now ~40 us)

Step3: Issue SOFT_RESET: Write register - CONFIG_A (Address: 0x000; Value: 0xB0)

Step4: Wait for 1280 ns (as per specification, it needs to wait 750 ns)

Step4: Read INIT_STATUS: Read register - INIT_STATUS (Address: 0x030)

Step5: If INIT_DONE is '1', then Step 6 else Step4

Step6: Read VENDOR_ID: Read register - VENDOR_ID (Address: 0x00C)

Step7: If VENDOR_ID = 0x0451, then Step 8 else Issue ERROR

Step8: Stop JESD204: Write register - JESD_EN (Address: 0x200; Value: 0x00)

Step9: Stop Calibration: Write registers - CAL_EN (Address: 0x061; Value: 0x00)

Step10: Default to High Performance mode

Step11: JMODE selection: Write register - JMODE (Address: 0x201; Value: 0x09)

Step12: Desired KM1 value: Write register - KM1 (Address: 0x202; Value: 0x1F)

Step13: SYNC_SEL: Write register - JCTRL (Address: 0x204; Value: 0x03)

Step14: Calibration settings: Write register - CAL_CFG0 (Address: 0x062; Value: 0x01)

Step15: Calibration settings: Write register - CAL_CFG1 (Address: 0x065; Value: 0x01)

Step16: Enable TRIGOUT: Write register - TRIGOUT_CTRL (Address: 0x057; Value: 0x81)

C_PLL is disabled, so not reading VCO_CAL_STATUS register at this time

Step17: Enable Calibration: Write register - CAL_EN (Address: 0x061; Value: 0x01)

Step18: Enable Over-range: Write register - OVR_CFG (Address: 0x213; Value: 0x0F)

Step19: Re-start JESD204: Write register - JESD_EN (Address: 0x200; Value: 0x01)

Step20: Enable Calibration: Write register - CAL_PIN_CFG (Address: 0x06B; Value: 0x01)

Step21: Set CALTRIG = '0' (For how long this should be low ? Right now 5.1 us)

Step22: Set CALTRIG = '1' (For how long this should be high ? Right now it will be high till CALSTAT = '1')

If CALSTAT = '1', then CALTRIG <= '0';

FPGA Setup

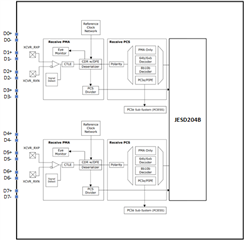

FPGA transceiver core can take only 4 Lanes, so 2 transceiver cores are used to make 8 lanes.

Configuration of Transceiver Core

Configuration of JESD204BRX Core

Please let me know if you have any questions or concerns.

Please let me know your thoughts:

Thanks

Madhu