Other Parts Discussed in Thread: TIDA-01504,

Tool/software:

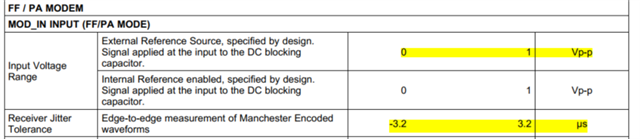

I am developing a fieldbus application using the DAC8742H. The transmitter driver board was taken from the DAC8742H datasheet. However, when I went through the Physical layer tests, it failed at the Receive Jitter tolerance test. I believe the problem is from the DAC8742H itself, because the BUS+ was connected directly to the MOD_IN of the DAC8742H (via DC removal capacitor). I checked the DAC8742H datasheet and found out the jitter tolerance is +-3.2us

However, when setting the jitter of my reference transmitter to 3.2us, the DAC8742H gets only 95-97% of every 1000 transmitted messages.

So my question is:

- Is there any "margin of safety" for the 3.2us jitter tolerance stated in the datasheet? For example, how likely/many percentages, we receive a message correctly if the jitter is 3.21us?

- Is the DAC8742H, or any relevant design, like TIDA-01504, passed the Physical layer test?