Other Parts Discussed in Thread: LMK04826, AFE58JD48

Tool/software:

Hi,

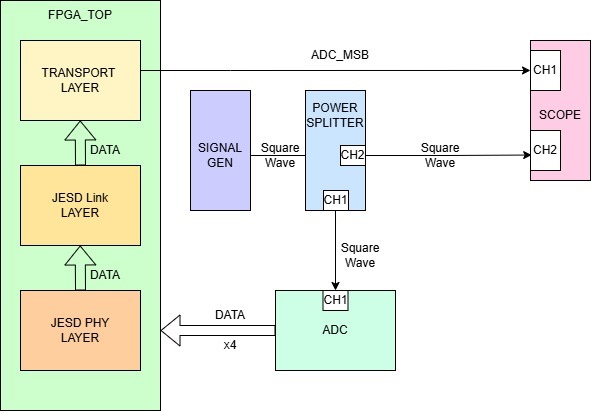

We planning to check the determinstic latency between JESD204B RX and ADC, I have a reference setup image we are planning to use for proving the deterministic latency.

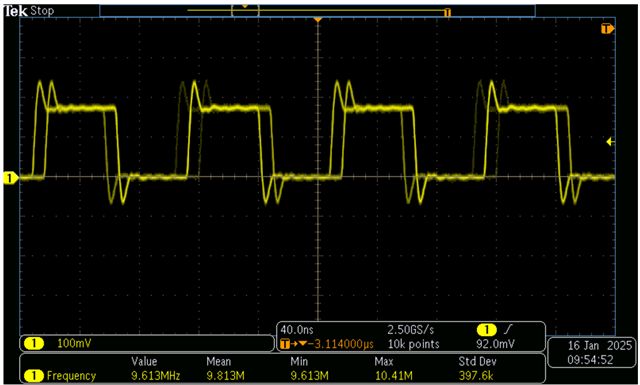

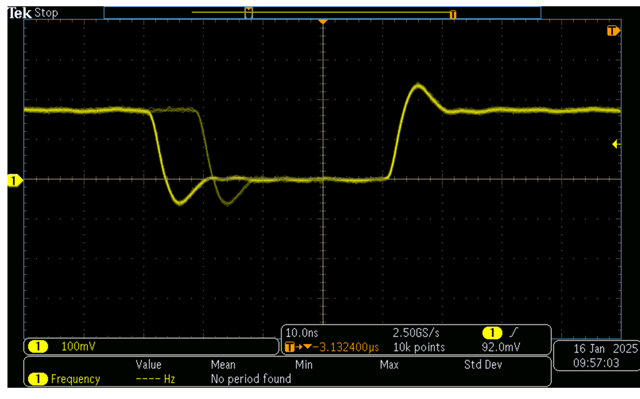

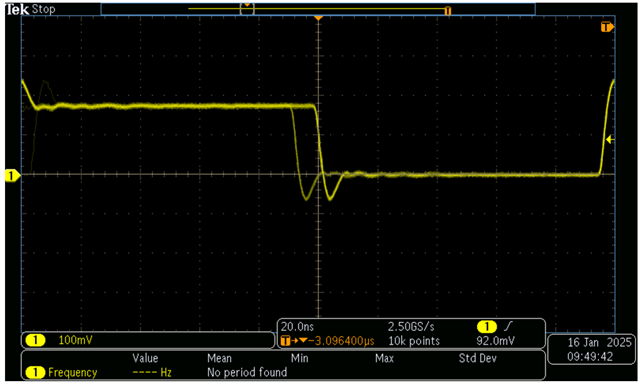

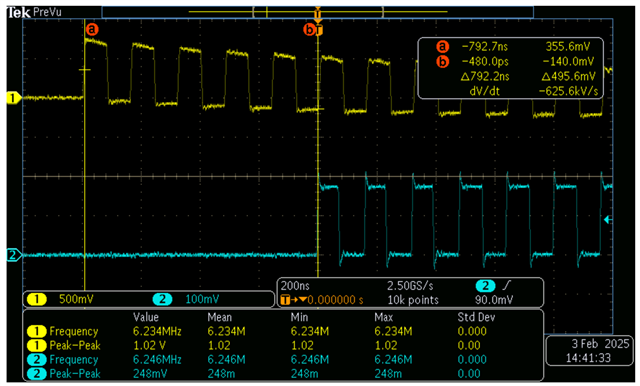

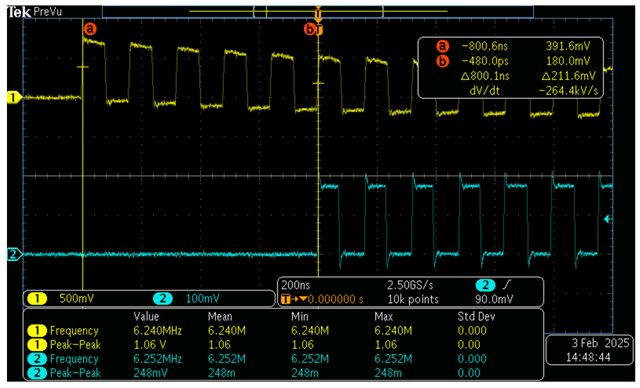

But we facing some issue with the ADC sample MSB bit, if we capture the ADC_MSB bit the duty cycle is not constant always, also the rising and falling edge have some overlapping.

We are sending a sine wave as input to at different frequencies for testing but as we increase the frequency the overlapping increases. So can help us to debug this issue since if the duty is not constant we cannot say the signal is relaible for use to prove deterministic latency. I have attached the capture images at 5MHz.

5MHz