- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

Tool/software:

Hi all

My customer plans to be using 3 x ADC3421IRTQR and they have this question:

Is it ok to drive the 3 ADCs with the same clock ?

(Pin 21 und Pin 22)

Best regards

Ueli

--------------------------

ADC3421 Quad-channel 12-bit 25-MSPS analog-to-digital converter (ADC) ADC3421IRTQR

Hi Ue,

Yes you can do that, but you wan to use a clock buffer to appropriately make copies of the sampling clock.

Something like the CDCLVP2102 or similar will work.

Regards,

Rob

Hi Rob

Thank you for the quick reply and for pointing to:

CDCLVP2102 Low jitter, dual 1:2 universal-to-LVPECL buffer CDCLVP2102RGTR

Just to make sure I understand you correctly:

Does this mean you recommend to use a buffer in front of every ADC clock input, meaning using 3 buffers ?

Best regards

Ueli

Hi Ueli,

What I am saying is take the main clock and use a 1:2 or 1:4 clock buffer in order to drive each ADC clock input pins.

The CDC device I recommended above was just an example.

I will loop in the CTS clocking team to help down select a suitable device.

Regards,

Rob

Hi Ueli,

Can you proivde more details as to what input/output format you require here as well as frequency?

I quickly glanced the ADC DS and it looks like the frequency in quesiton is somewhere between 15-125MHz? Nevertheless, I rather confirm than assume.

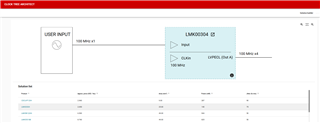

I see talk about CDCLVPxxxx so it an LVPECL clock is required I agree with Rob and a device like CDCLVP1204 or LMK00304 are viable options.

For future reference we also have a tool, Clock tree architect where you can input your clocking requirements to generate a list of potential solutions.

Inputting 4-100MHz LVPECL output & a 100MHz input results in the following results:

Best regards,

Vicente

Vicente

As the customer will be using the 25Msps variant we are looking at 25MHz clock.

Thank you for pointing to:

CDCLVP1204 Low-jitter, two-input, selectable 1:4 universal-to-LVPECL buffer CDCLVP1204RGTR

-------------------------------

Rob

Thank you for looping in our CTS clocking team.

As the ADC3421 integrates a clock buffer: Are individual external buffers really required ?

Best regards

Ueli

Ueli,

Yes, most definitely. But for clarity, send over a detailed block diagram on what you are proposing without a clock buffer/splitter.

Regards,

Rob

Rob

Checking with the customer they dont yet have a schematic but are fine with the comments provided, so we can close this thread.

Best regards

Ueli