Other Parts Discussed in Thread: ADS7866, OPA333, , ADS7042, TLV333, TLA2518, ADS7138

Tool/software:

I initial wrote this just to ask for information to question 3 below, but it turned into a more design review. If i should go through my TI FAE please let me know. thanks.

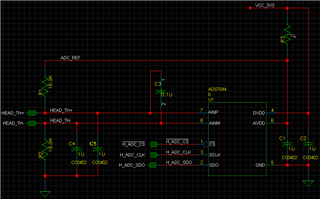

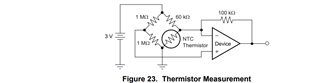

i have a Thermistor I cannot change at the end of a 12" cable.

Its resistance is 23k-127k, i'm most concerned about it over the 23k-52k range

so i've chosen the pullup value to be ~34k

the cable causes SI issue where noise is injected, about 50khz, 200mv P-P

the solution i've come up with is something like this:

1) I split the pullup into pull up and pull down so that AINM doesn't go below GND, is this necessary? any problems with this?

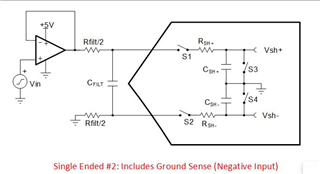

2) I expect the differential input generally deal with the noise, is this correct?

3) I would like to understand the input load of this device, i see in figure 33 the model of the input. if the input is not changing, is the voltage at Cs+ and Cs- stable, or does initiating a sample cause any load / voltage to change? (i ask because the current through the thermistor is very small,

4) Is this a good solution or can you recommend a better one?

5) i've also added tvs diodes to the th+/- lines as they connect to external connector and wire.

6) i would expect that i do not need C4 & C5, but can add them to avert risk (to appease boss)

7) since this circuit always results in a positive signal, then this is similar to an 11 bit single ended. i assume that if i sample very quickly, i can accumulate values and do averaging like other ADC to increase the effective number of bits? or i could replace with

8) a coworker had recommended using an OPA333 to buffer the input signal into a ADS7866 and used an external reference source. I feel that the solution i came up with is much cleaner, cheaper, and will result in better measurements, but they are more senior and risk averse. opinion?

Any thoughts and suggestions are welcome. thank you.

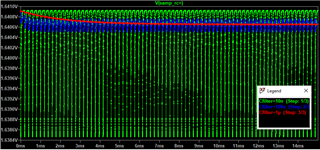

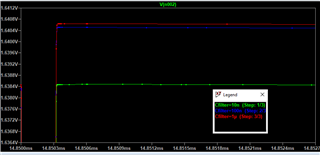

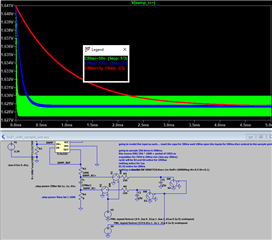

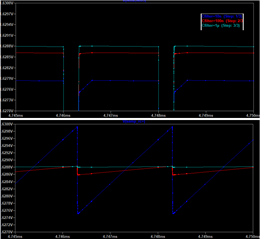

the bottom is the external pin model, so while the smallest cap recovers quickest, it also drains the fastest.

the bottom is the external pin model, so while the smallest cap recovers quickest, it also drains the fastest.