Part Number: ADS1247

Tool/software:

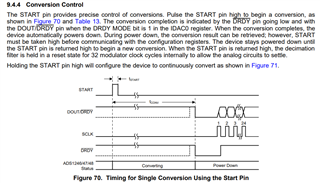

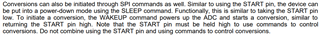

I am trying to optimize current by keeping only enabling START high only when necessary. I am not using DRDY just waiting the appropriate time after START to read the data as per the sampling rate.

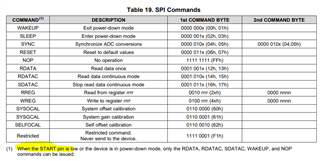

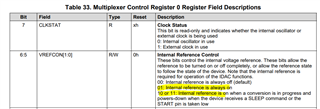

I am not sure how START and sending the SYNC command work together along with when data conversion occurs. I would like to know if I will get valid data by performing the tasks as follows with the settings PGA128 and 1000 SPS:

- START HIGH

- wait 7uS (much greater than 3x tosc)

- send SYNC Command

- START LOW

- Wait 3mS (spec calls for 1.138ms min for conversion, time is not an issue here)

- Read data

It is not clear if a conversion will take place since START was pulled low after the SYNC command. Would I have to send SYNC command first and then START HIGH? It is not clear that if start is turned off after sync if the converter will provide an accurate conversion. Will START have to be taken high again after the SYNC Command in order for a conversion to take place? Or will it occur after the end of SYNC when START is low?