Other Parts Discussed in Thread: ADS131B04-Q1EVM

Tool/software:

Hi Ti Support Team,

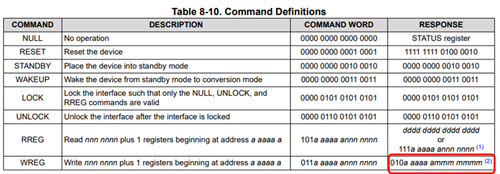

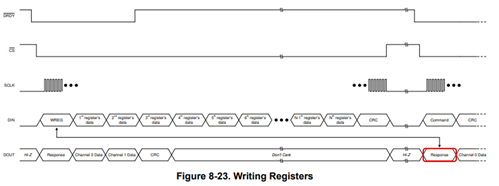

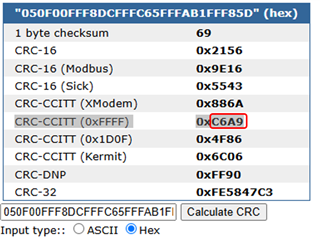

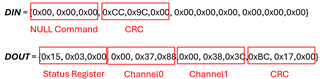

I am currently using the CH1_CFG setting to 10b (Positive DC test signal) to output a test signal and calculate Vref. This is primarily for use in the initial-stage inspection process, to check if the Vref value is within normal limits. However, after outputting the test signal and calculating Vref, when I change the CH1_CFG setting to 00b (AIN1P and AIN1N), the ADS131B02 encounters an issue. Both the WREG and RREG commands are not functioning correctly.

Could you please guide me on the correct procedure to handle this situation? I would appreciate your assistance in resolving this issue.

Thank you for your support.

BR

Stephen