Other Parts Discussed in Thread: ADS5295

Tool/software:

Hello,

I am using ADS5295 EVAL Board. I converted the P10 connector to headers and entered the pins of the ALINX AC7020C card with twisted cables.

I want to work with 2-wire communication, 12bit resolution and 1/4 sample settings.

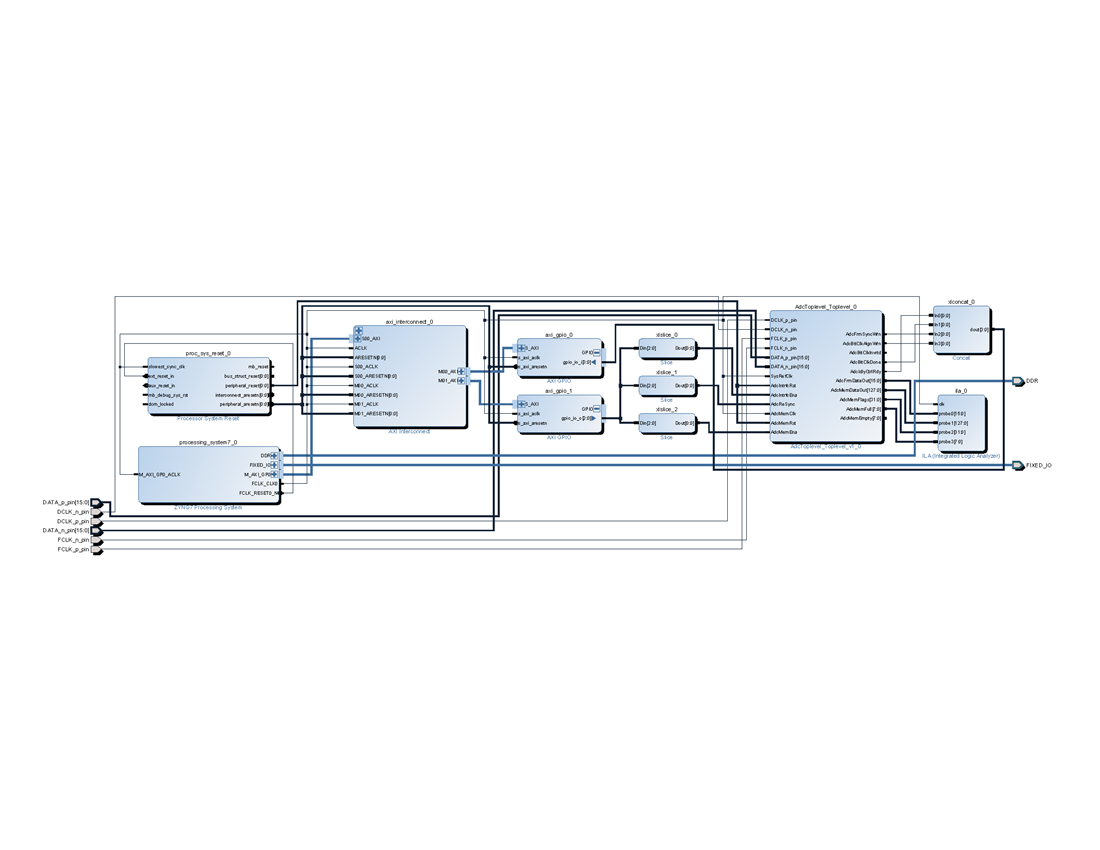

I downloaded the file from the link in the xapp524 document (secure.xilinx.com/.../clickthrough.do and created a Custom IP in vivado. Then I made the connections and entered the configurations.

Connections:

ADC IP Configuration:

I also specified my pins in my XDC file and made synthesis.

##LCLK_P PIN (DCLK)

set_property PACKAGE_PIN J18 [get_ports DCLK_p_pin]

set_property IOSTANDARD LVDS_25 [get_ports DCLK_p_pin]

##LCLK_N PIN (DCLK)

set_property PACKAGE_PIN H18 [get_ports DCLK_n_pin]

set_property IOSTANDARD LVDS_25 [get_ports DCLK_n_pin]

##FCLK_P PIN (ADCLK)

set_property PACKAGE_PIN L16 [get_ports FCLK_p_pin]

set_property IOSTANDARD LVDS_25 [get_ports FCLK_p_pin]

##FCLK_N PIN (ADCLK)

set_property PACKAGE_PIN L17 [get_ports FCLK_n_pin]

set_property IOSTANDARD LVDS_25 [get_ports FCLK_n_pin]

#ADC_CHANNEL1_0

set_property PACKAGE_PIN K17 [get_ports {DATA_p_pin[0]}]

set_property IOSTANDARD LVDS_25 [get_ports {DATA_p_pin[0]}]

set_property PACKAGE_PIN K18 [get_ports {DATA_n_pin[0]}]

set_property IOSTANDARD LVDS_25 [get_ports {DATA_n_pin[0]}]

#ADC_CHANNEL1_1

set_property PACKAGE_PIN K19 [get_ports {DATA_p_pin[1]}]

set_property IOSTANDARD LVDS_25 [get_ports {DATA_p_pin[1]}]

set_property PACKAGE_PIN J19 [get_ports {DATA_n_pin[1]}]

set_property IOSTANDARD LVDS_25 [get_ports {DATA_n_pin[1]}]

#ADC_CHANNEL2_0

set_property PACKAGE_PIN H16 [get_ports {DATA_p_pin[2]}]

set_property IOSTANDARD LVDS_25 [get_ports {DATA_p_pin[2]}]

set_property PACKAGE_PIN H17 [get_ports {DATA_n_pin[2]}]

set_property IOSTANDARD LVDS_25 [get_ports {DATA_n_pin[2]}]

#ADC_CHANNEL2_1

set_property PACKAGE_PIN B19 [get_ports {DATA_p_pin[3]}]

set_property IOSTANDARD LVDS_25 [get_ports {DATA_p_pin[3]}]

set_property PACKAGE_PIN A20 [get_ports {DATA_n_pin[3]}]

set_property IOSTANDARD LVDS_25 [get_ports {DATA_n_pin[3]}]

#ADC_CHANNEL3_0

set_property PACKAGE_PIN F19 [get_ports {DATA_p_pin[4]}]

set_property IOSTANDARD LVDS_25 [get_ports {DATA_p_pin[4]}]

set_property PACKAGE_PIN F20 [get_ports {DATA_n_pin[4]}]

set_property IOSTANDARD LVDS_25 [get_ports {DATA_n_pin[4]}]

#ADC_CHANNEL3_1

set_property PACKAGE_PIN G17 [get_ports {DATA_p_pin[5]}]

set_property IOSTANDARD LVDS_25 [get_ports {DATA_p_pin[5]}]

set_property PACKAGE_PIN G18 [get_ports {DATA_n_pin[5]}]

set_property IOSTANDARD LVDS_25 [get_ports {DATA_n_pin[5]}]

#ADC_CHANNEL4_0

set_property PACKAGE_PIN J20 [get_ports {DATA_p_pin[6]}]

set_property IOSTANDARD LVDS_25 [get_ports {DATA_p_pin[6]}]

set_property PACKAGE_PIN H20 [get_ports {DATA_n_pin[6]}]

set_property IOSTANDARD LVDS_25 [get_ports {DATA_n_pin[6]}]

#ADC_CHANNEL4_1

set_property PACKAGE_PIN G19 [get_ports {DATA_p_pin[7]}]

set_property IOSTANDARD LVDS_25 [get_ports {DATA_p_pin[7]}]

set_property PACKAGE_PIN G20 [get_ports {DATA_n_pin[7]}]

set_property IOSTANDARD LVDS_25 [get_ports {DATA_n_pin[7]}]

#ADC_CHANNEL5_0

set_property PACKAGE_PIN H15 [get_ports {DATA_p_pin[8]}]

set_property IOSTANDARD LVDS_25 [get_ports {DATA_p_pin[8]}]

set_property PACKAGE_PIN G15 [get_ports {DATA_n_pin[8]}]

set_property IOSTANDARD LVDS_25 [get_ports {DATA_n_pin[8]}]

#ADC_CHANNEL5_1

set_property PACKAGE_PIN K14 [get_ports {DATA_p_pin[9]}]

set_property IOSTANDARD LVDS_25 [get_ports {DATA_p_pin[9]}]

set_property PACKAGE_PIN J14 [get_ports {DATA_n_pin[9]}]

set_property IOSTANDARD LVDS_25 [get_ports {DATA_n_pin[9]}]

#ADC_CHANNEL6_0

set_property PACKAGE_PIN N15 [get_ports {DATA_p_pin[10]}]

set_property IOSTANDARD LVDS_25 [get_ports {DATA_p_pin[10]}]

set_property PACKAGE_PIN N16 [get_ports {DATA_n_pin[10]}]

set_property IOSTANDARD LVDS_25 [get_ports {DATA_n_pin[10]}]

#ADC_CHANNEL6_1

set_property PACKAGE_PIN L14 [get_ports {DATA_p_pin[11]}]

set_property IOSTANDARD LVDS_25 [get_ports {DATA_p_pin[11]}]

set_property PACKAGE_PIN L15 [get_ports {DATA_n_pin[11]}]

set_property IOSTANDARD LVDS_25 [get_ports {DATA_n_pin[11]}]

#ADC_CHANNEL7_0

set_property PACKAGE_PIN M14 [get_ports {DATA_p_pin[12]}]

set_property IOSTANDARD LVDS_25 [get_ports {DATA_p_pin[12]}]

set_property PACKAGE_PIN M15 [get_ports {DATA_n_pin[12]}]

set_property IOSTANDARD LVDS_25 [get_ports {DATA_n_pin[12]}]

#ADC_CHANNEL7_1

set_property PACKAGE_PIN K16 [get_ports {DATA_p_pin[13]}]

set_property IOSTANDARD LVDS_25 [get_ports {DATA_p_pin[13]}]

set_property PACKAGE_PIN J16 [get_ports {DATA_n_pin[13]}]

set_property IOSTANDARD LVDS_25 [get_ports {DATA_n_pin[13]}]

#ADC_CHANNEL8_0

set_property PACKAGE_PIN C20 [get_ports {DATA_p_pin[14]}]

set_property IOSTANDARD LVDS_25 [get_ports {DATA_p_pin[14]}]

set_property PACKAGE_PIN B20 [get_ports {DATA_n_pin[14]}]

set_property IOSTANDARD LVDS_25 [get_ports {DATA_n_pin[14]}]

#ADC_CHANNEL8_1

set_property PACKAGE_PIN E17 [get_ports {DATA_p_pin[15]}]

set_property IOSTANDARD LVDS_25 [get_ports {DATA_p_pin[15]}]

set_property PACKAGE_PIN D18 [get_ports {DATA_n_pin[15]}]

set_property IOSTANDARD LVDS_25 [get_ports {DATA_n_pin[15]}]

set_property BEL BUFR [get_cells design_1_i/AdcToplevel_Toplevel_0/U0/AdcToplevel_Toplevel_I_AdcToplevel/AdcToplevel_I_AdcClock/Gen_Bufr_Div_3.AdcClock_I_Bufr]

set_property LOC BUFR_X1Y10 [get_cells design_1_i/AdcToplevel_Toplevel_0/U0/AdcToplevel_Toplevel_I_AdcToplevel/AdcToplevel_I_AdcClock/Gen_Bufr_Div_3.AdcClock_I_Bufr]

But the BRAM usage was around 236%. Is this normal, where am I doing wrong?

If I can overcome this problem, I will have other questions :)