Tool/software:

Hi

Has anyone been able to interface via SPI an ATMEGA2560 to an ADS8568?

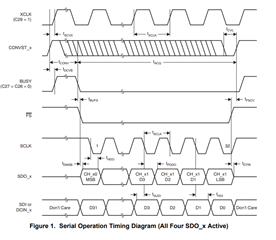

In my current application, the ADS8568 is layout to operate in serial mode.

Until now I have been unsuccessful in getting readings back on the MISO line.

After looking at the spec sheet for ADS8568, it's timing requirements appear to be a lot more demanding than what the ATMEGA2560 can do.

(It looks like it was made to work with C2000 or FPGAs)

For example this :

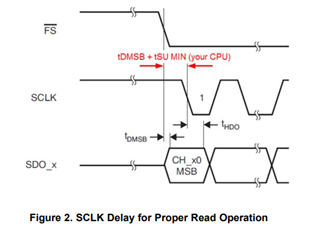

Care should be taken to ensure that the delay time of

the most significant bit (tDMSB) from the falling edge of FS/CS is met before applying the serial clock. This

delay is specified as 12 ns MAX

Since ATMEGA works at 16MHZ, its fastest instruction will be in 62nS!

Am I right in thinking the ATMEGA2560 will not be able to communicate via SPI to the ADS8568?

Any help would be appreciated.