Part Number: ADS8568

Hi Team,

The customer is having issues with the ADC SPI communication. Kindly refer to the information below:

I can read te data but from time to time the ADC « fails » to convert data.

I follow the datasheet and code a SPI in a FPGA to get the data from the ADC.

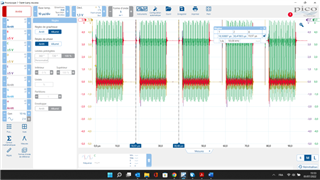

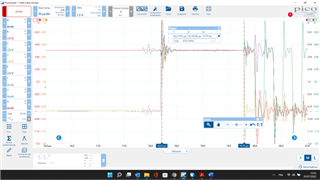

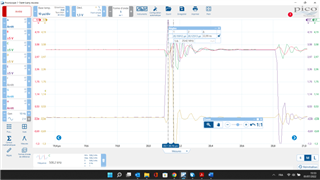

So I send a conversion request on CONSTA, B, C and D at the same time, then wait for Busy to drop and put 0 on FS to read the data on SDO_A, B, C and D. The SCLK is generated only when the data are red from the FPGA.

SCLK = 2,75 MHz -> clock to synchronize the data on SDOA, B, C , D

Conv Clk = 50 kHz -> frequency to initiate a conversion sequence

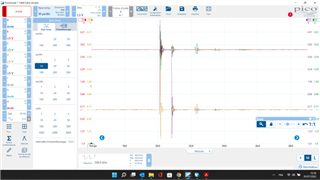

Green trace : SCLK

Red trace : FS

Blue trace : CONVST

Brown trace : Busy

The two first pictures show the correct behaviour, I can read the data correct

The Following picture show the signals when the conversion fails. Busy picks up for a couple of ns an drops immedialtely, apparently the conversion fails as I can’t imagine that the conversion is so fast. It takes usually (on a successful conversion) around 2 µs to make a conversion.

I don’t think the ADC has an issue, there is probably something I am missing. Any advice help would be highly appreciated.

I hope you can help the customer.

Thanks!

Regards,

Marvin