Tool/software:

Hello, experts from TI. I'd like to consult you about AFE58JD32.

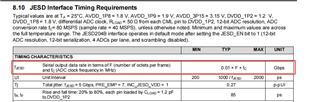

According to the chip manual, the line rate calculation formula of jesd output is 0.01xFxfc

(fs = fc)

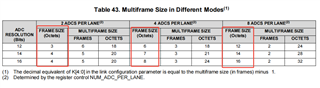

The value of F is related to the number of lane and the ADC resolution

The above part is a screenshot I took from the chip manual.

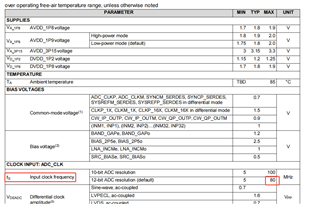

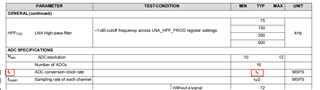

We set the clock of AFE at 80 MHz, configured in 4 ADCS PERLANE mode, and the ADC resolution is 12 bits. According to the chip manual, we can determine that the value of F is 6 and the value of fc is 80 Msps.

Therefore, under this configuration, the line rate calculation result of JESD is 4.8 Gbps.

IF We set the clock of AFE at 80 MHz, configured in 8 ADCS PERLANE mode, and the ADC resolution is 12 bits. According to the chip manual, we can determine that the value of F is 12 and the value of fc is 80 Msps.

Therefore, under this configuration, the line rate calculation result of JESD is 9.8 Gbps. In this situation, the line rate achieved was 9.8 Gbps, which has exceeded 5 Gbps. This is quite confusing. Is there a problem with the understanding? Could a TI expert please help clarify it for me? Thank you.