Tool/software:

Dear Sir

We are having synchronising issues on the AFE data.

We suspect it is the AFE not resetting correctly.

We follow the device initialization as per the documentation:

Device Initialization

After bringing up all the supplies and applying a RESET signal, follow these steps to initialize the device:

1. Write all bits marked 1 in all the register maps (which is only 5 bits: reg 3, D1, D4)

2. The following steps initialize the PLL:

1. 100 μs or later after the clock starts and after applying RESET, write the PLLRST1 and PLLRST2 bits to 1

2. Wait for at least 10 μs and then write the PLLRST1 and PLLRST2 bits to 0

Above PLL initialization must be done whenever the device comes out of a global power-down mode or

when ADC_CLK is switched off and turns on again.

3. Apply a TX_TRIG pulse to synchronize operation across multiple devices.

However in 1% of reset cases, the data from the various channels may be unsynchronised.

This occurs even at very low speeds (with a 10MHz AFE clock)

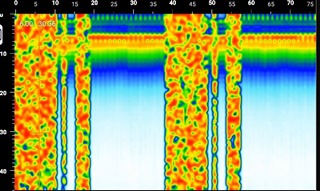

As per the SWAROOP board, with 2 AFE, and 4 TX, if we display the data as a B-Scan, we can see the error as per the attached image.

Here we have channels 1 to 128.

Channels 1 to 32 and 64 to 96 are the same AFE channels due to symmetry.

Has this issue been identified by anyone else?