Tool/software:

Hey everyone,

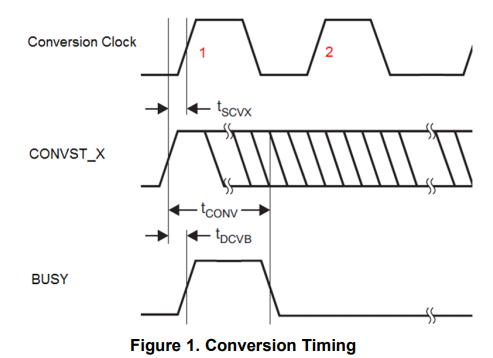

I'm coming from the stm32 ecosystem and the issue i have is that interfacing with the ads8568 I'll only be able to run a single data line SPI of around 45Mhz and with the high end H7 series I can hit 100 Mhz.

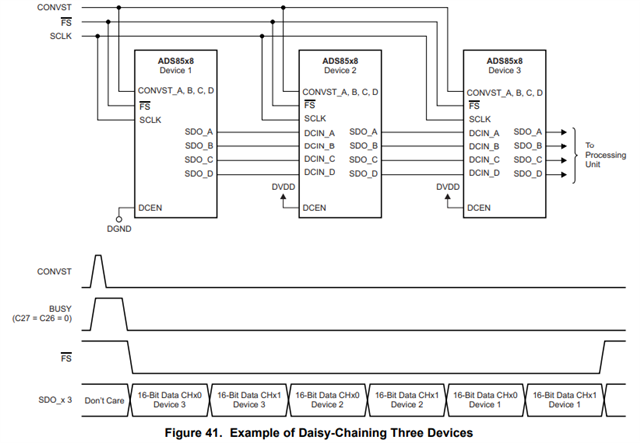

For my application I am running three ADS8568 in a daisy chain and even running an fpga/cpld i'll still be limited by the spi line.

In addition I want to store the data in an sd card and then push it to the cloud via a lte module.

I assume that to run the max data rate I'll need to interface with only an fpga.

Whats the max sample rate that can be achieved interfacing the ADS8568 with a MCU and would SPI be the recommended communication method?

Thanks in advance