Other Parts Discussed in Thread: DAC8830, , TPS3840, TL431, DAC8740H

Tool/software:

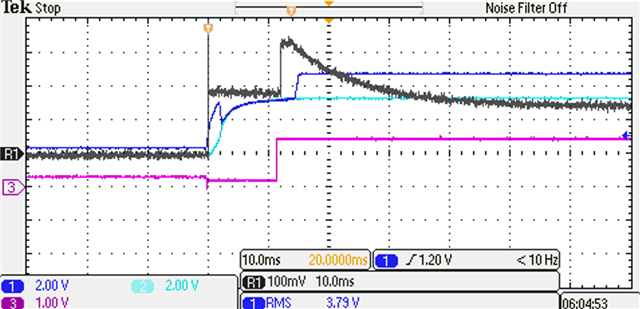

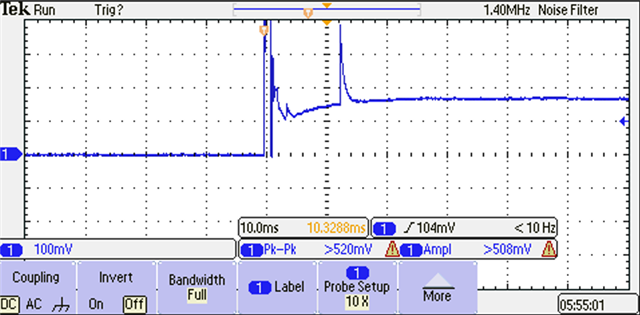

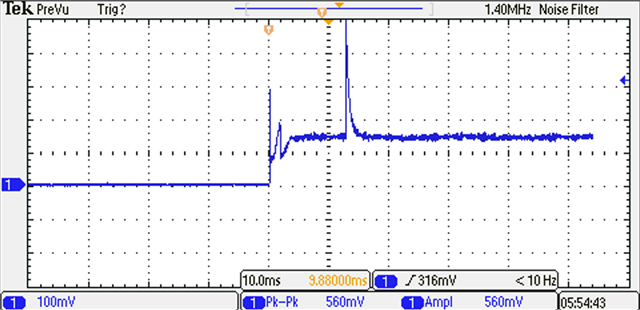

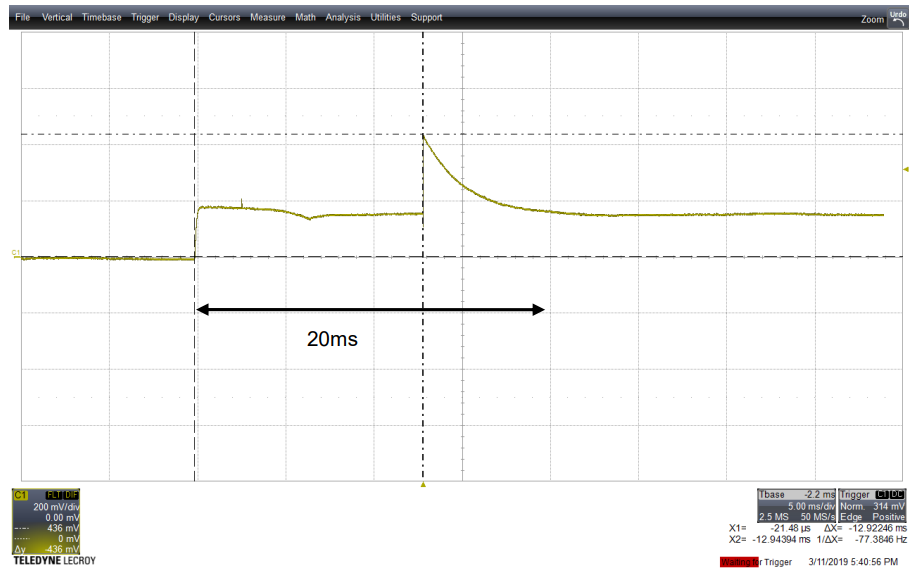

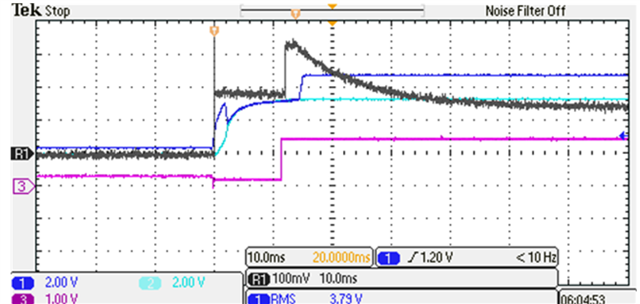

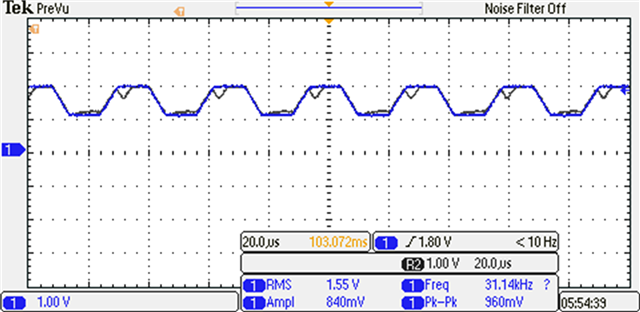

My MOD_OUT signal get distorted when changing from using internal (blue) to external (black) reference.(REF_EN was selected accordingly)

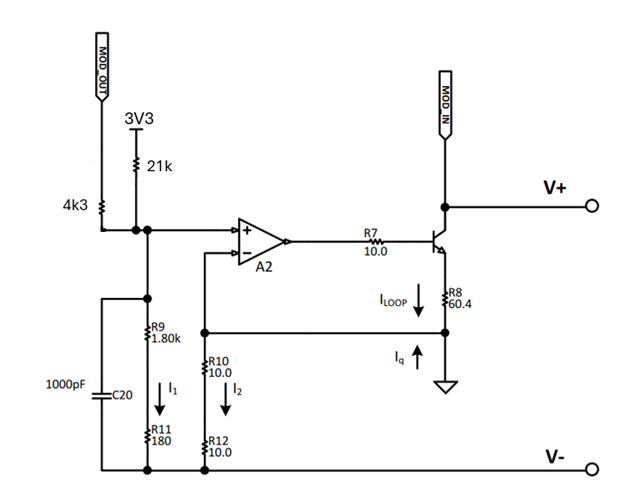

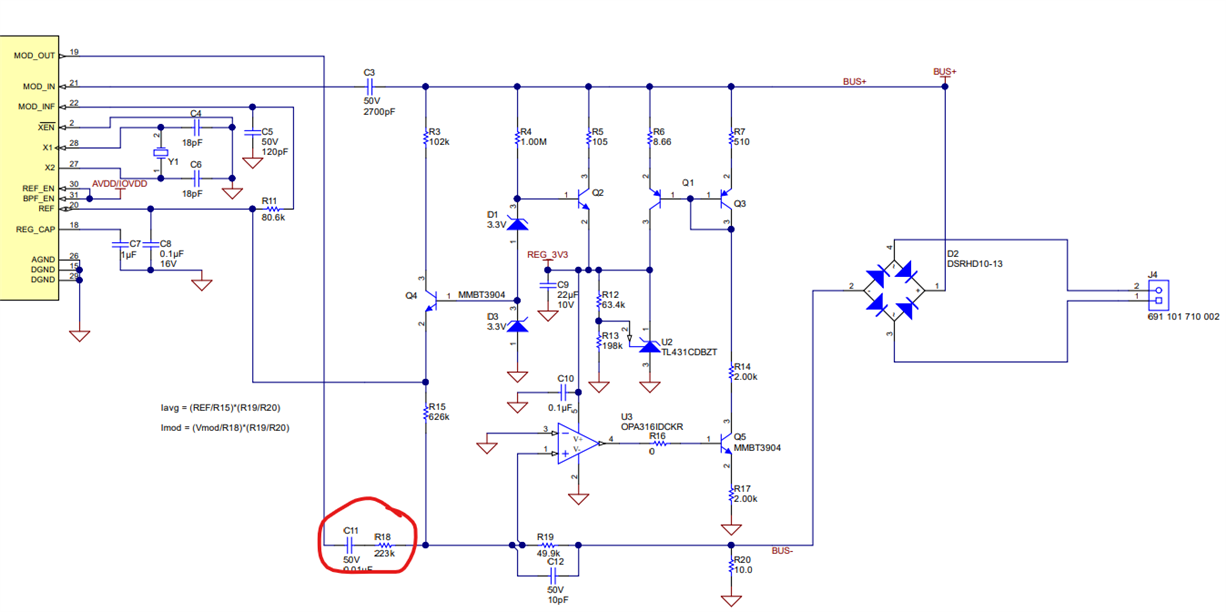

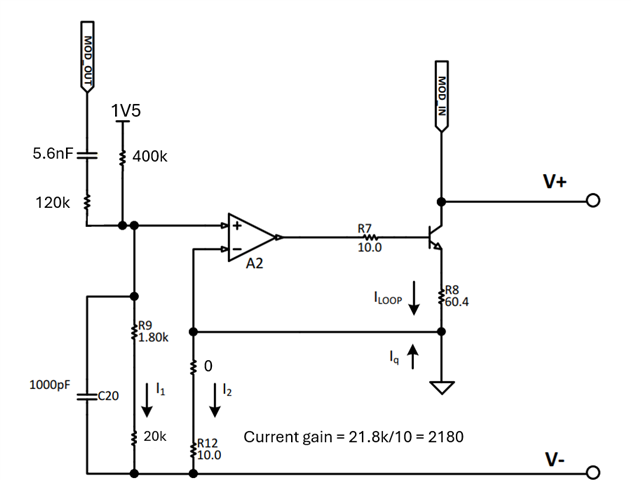

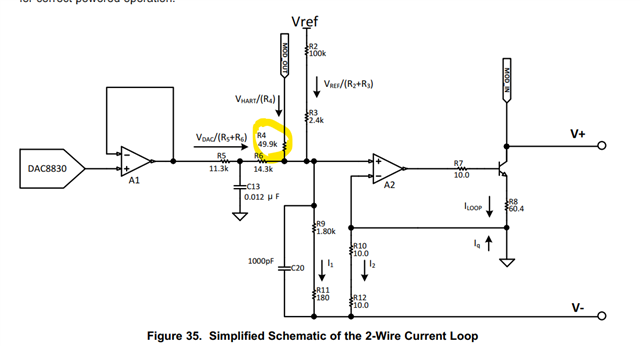

The MOD_OUT signal drive the 2-wire current loop circuit as suggesting in the DAC8742H datasheet

When I disconnect the MOD_OUT from the 2-wire current loop circuit (remove R4), the MOD_OUT signal is OK with external ref

When I reduce the FF current by increase R4, the MOD_OUT signal is OK with external ref

When I increase the input external ref, from 2V5 to 3V3, the signal was also OK with external ref

So my questions are:

- More details about the external reference internal electrical characteristic (max/min input current, input impedance)

- Any specific case where we should only use external ref

- Will the chip damaged if I use 3V3 for the external ref