Other Parts Discussed in Thread: DAC5652, DAC5672, DAC5662

Tool/software:

Hi,

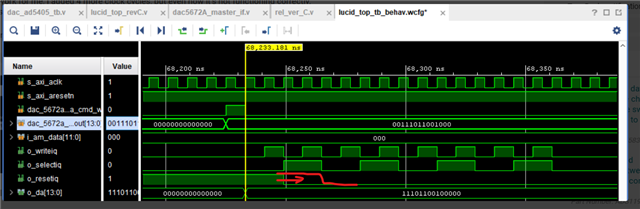

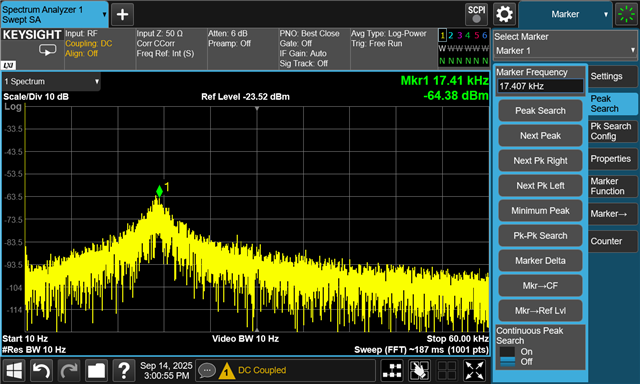

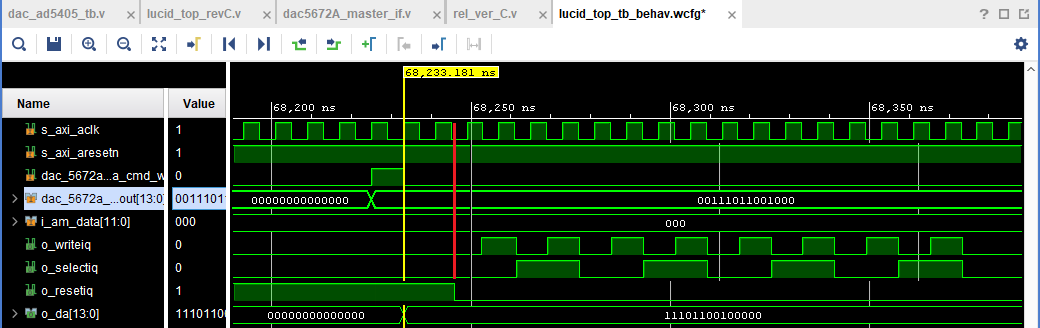

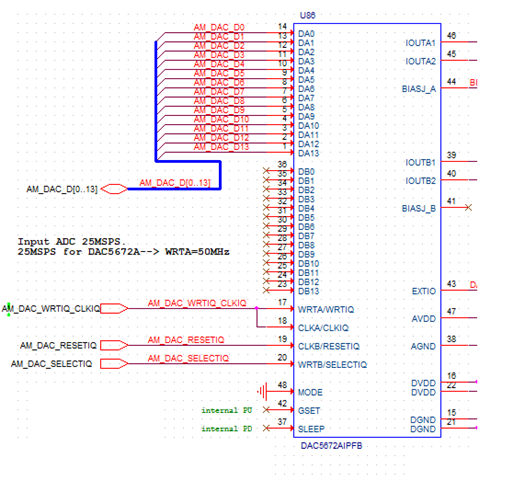

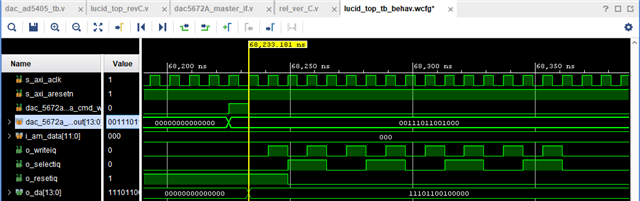

I’m trying to work with DAC5672A in Interleaved mode.

I’m writing the same data to both channels.

WRTIQ and CLKIQ are connected to the same line.

As I understand it, on the fourth rising edge of WRTIQ and CLKIQ, the data should enter.

After it didn’t work for me, I added 4 more clock cycles, but even now it’s not functioning correctly.

What is the issue?

Did I understand it wrong?

I also used below document (DAC5652, DAC5662 and DAC5672 Interleaved Data Mode).

dac5672a_X2_Interleaved_Mode .pdf

Thank you

Gil