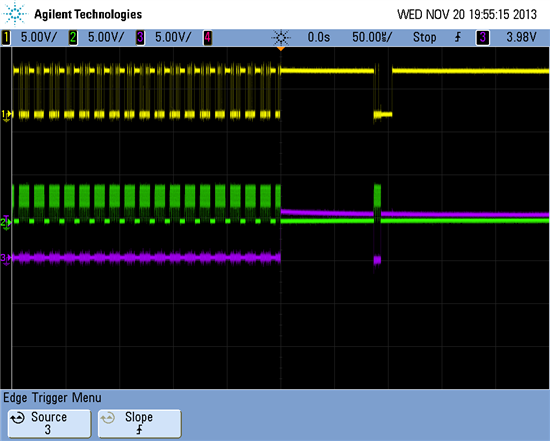

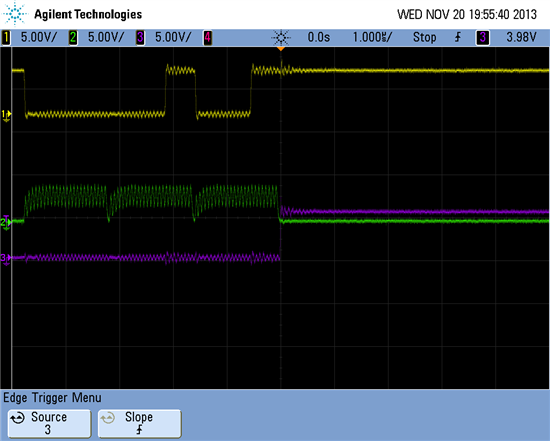

I'm using DAC8562 to generate ramp for VCO. But I encountered some problems with the SPI coding,

I did the power up and internal reference command before sending the data. But didn't see the 2.5V at the VREFIN/VREFOUT pin, and nothing output. Is there any standard process(command sequence) before the data sending?