Hello!

I need some advice with using ADC16DX370. I'm trying to evaluate set of KC705+[optional TSW14J10]+ ADC16DX370EVM with Xilinx JESD core. 1 lane mode is used; ADC is controlled via TI's GUI. Link is successfully established; SYNC is high and stable. But received data are corrupted in a very strange manner. When ADC Test Pattern (0x70[2]) is enabled four values are repeated: -31032,0, 31032,0. It differs from [0, 26280, 0, –26328] declared in the ADC's datasheet.

When any JESD Test Pattern is enabled (ramp with step 1 for example) it produce chaotic data with weak track of true sequence.

Changing TX Driver parameters have no affects to link stability or data corruption. Enabling scrambler do not improve results also. I tried JESD cores 6.1 and 6.2 (Vivado 2015.2, 2015.3) at line frequencies 7.4Gbps (maximum allowed for ADC) and 4.0Gbps with same results. Reference clock for FPGA is 1/2 of sampling rate (1/40 of lane speed). It is generated at EVM board. Timing constraints in FPGA project are met.

Several examples of data for ramp mode with step =1 :

f8d3, f8d2, f8d1, f8cf, f8d0, f8ce,..

e3e3, e3fd, e3e5, e3fe, e3ff, e3e5, fd00, fd01, fd02,..

04b8, 04a6, 04a5, 04bb, 04a3, 04bd, 04be, 04bf, 0460, 0461, 0462, 047c, 0464, 047a

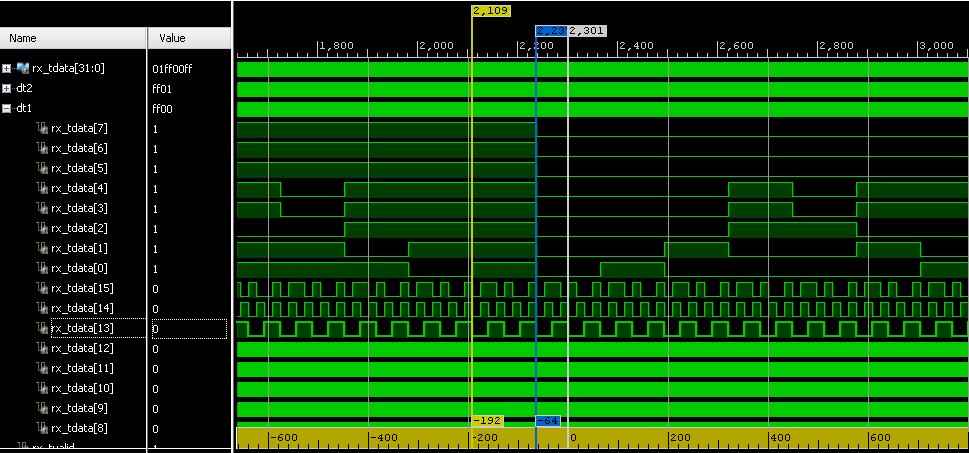

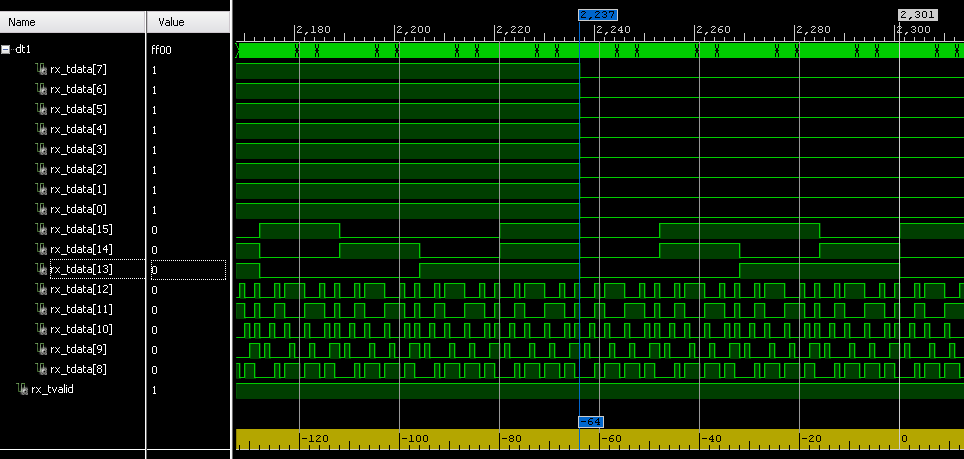

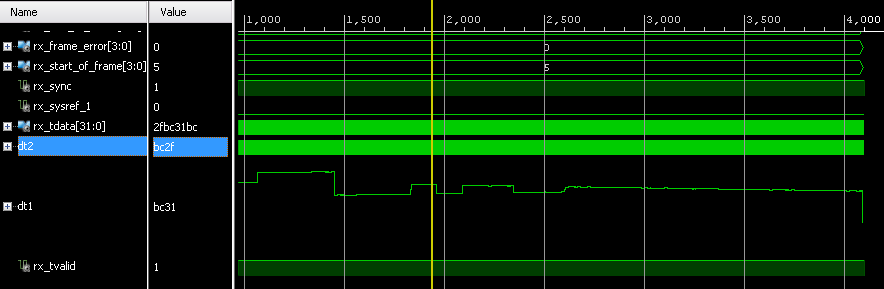

Examples of wave forms (with switching of high byte) is shown below

Please note that period of higher bits is power of 2 (64, 128, etc). They are not randomly changes at each sample. But they switches to incorrect values while counting. The only correct bit is 5 (it named as rx_tadata[13]).

So, it looks as parallel data corruption (not serial link corruption). Unfortunately I cannot determine the source of problem: ADC or Xilinx JESD core.

Could you make any suggestion, please? Thank you.

PS Important fact: same data sequence is repeated permanently. When Logic analyzer's trigger is set to any data value it captures same sequence everytime (for ramp pattern). For example:

ffe5, fffb, ffe3, fffd, fffe, ffff, 0000, 0001, 0002, 001c, 0004, 001a, 0019, 0007, 0008, 0016, ...