Hi all,

I’m using the Xilinx KC705 EVM and TI DAC37J82 EVM to evaluate JESD204 functionality.

First of all downloaded the Xilinx JESD204 Hardware demo project to the KC705. The demo project contains a 4-lane JESD TX-Core and a 4-lane JESD RX-Core and a JESD-PHY configured for near-PMA loopback mode. Everything works fine, TX & RX-JESD are in sync.

As a second step, I slightly modified the Xilinx JESD204 Hardware demo project to run in normal mode and configured the transceiver ports to the FMC pins as the .xdc file of the example design http://www.ti.com/lit/zip/slac690 .

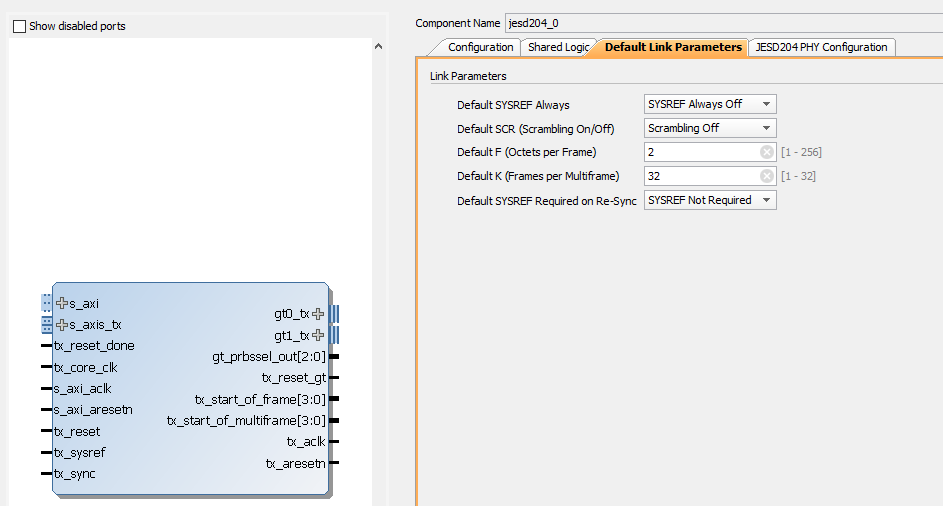

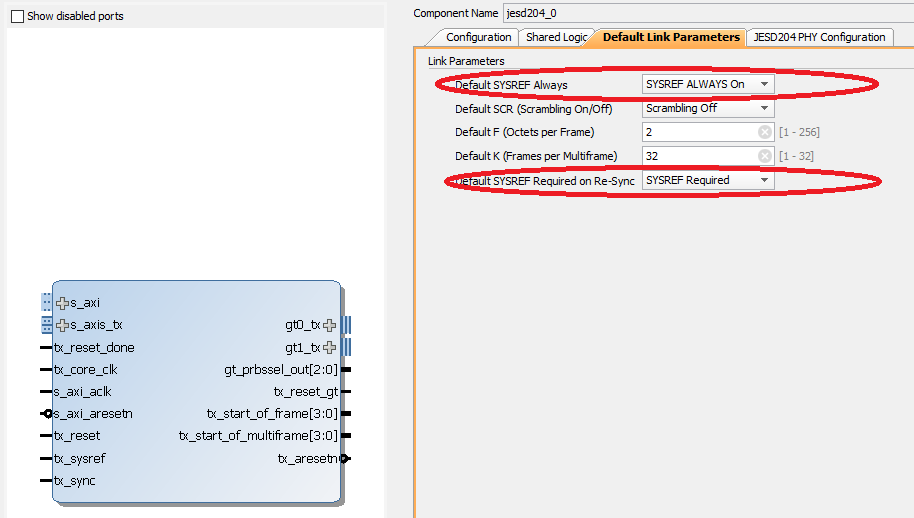

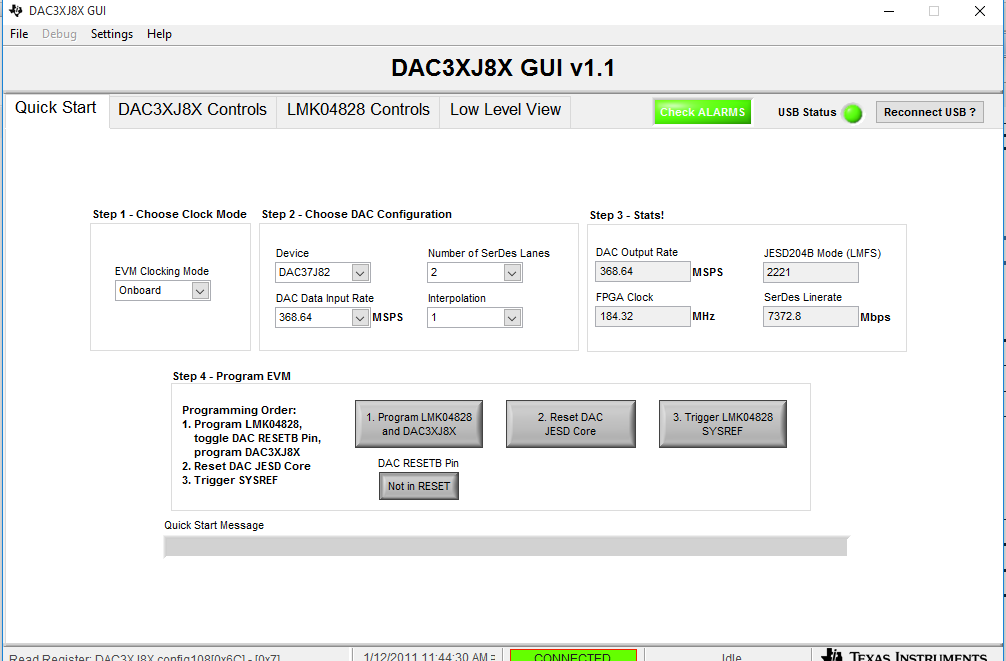

Here a screenshot of the Link parameters:

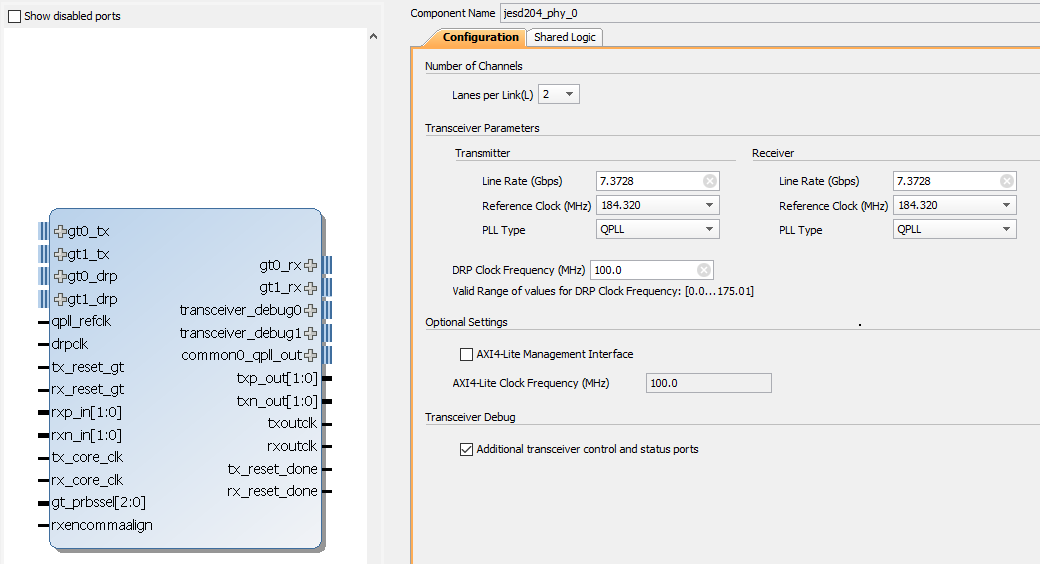

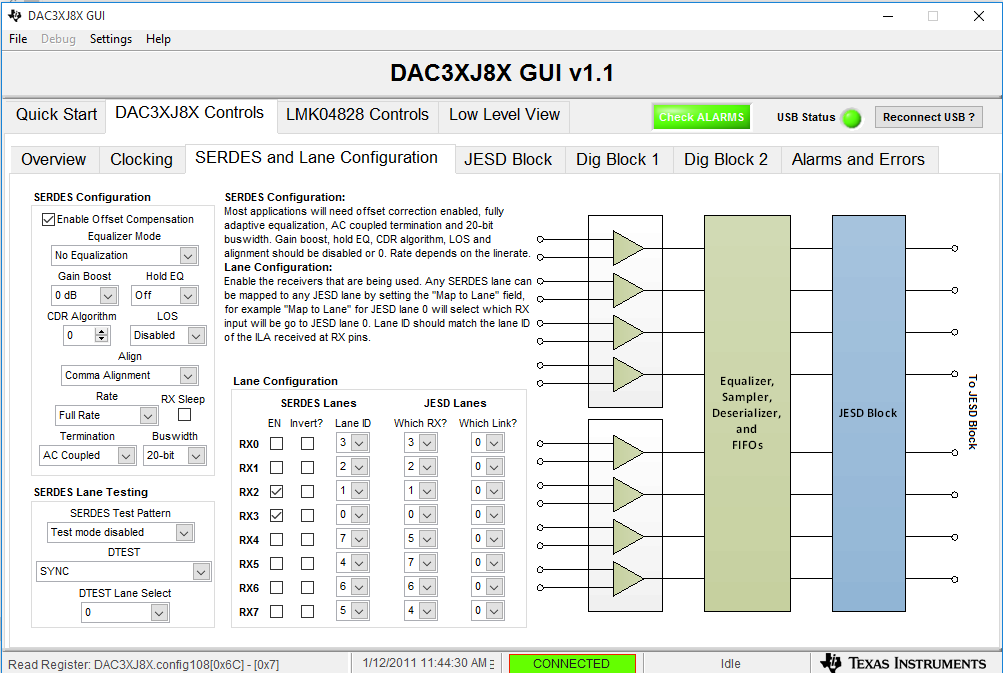

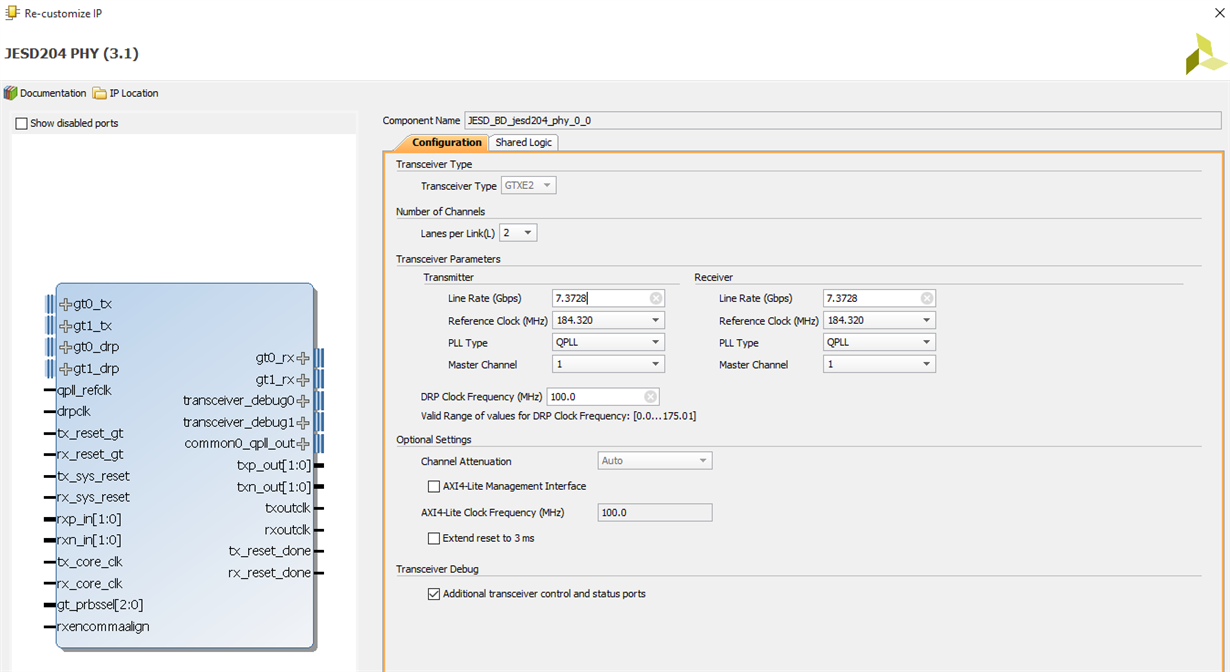

Here the screenshots of the JESD-PHY configuration:

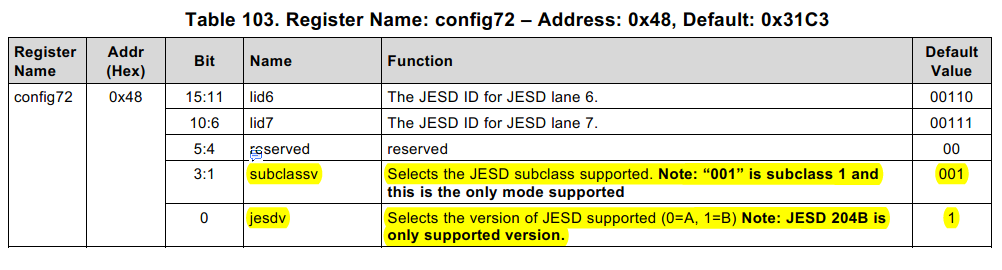

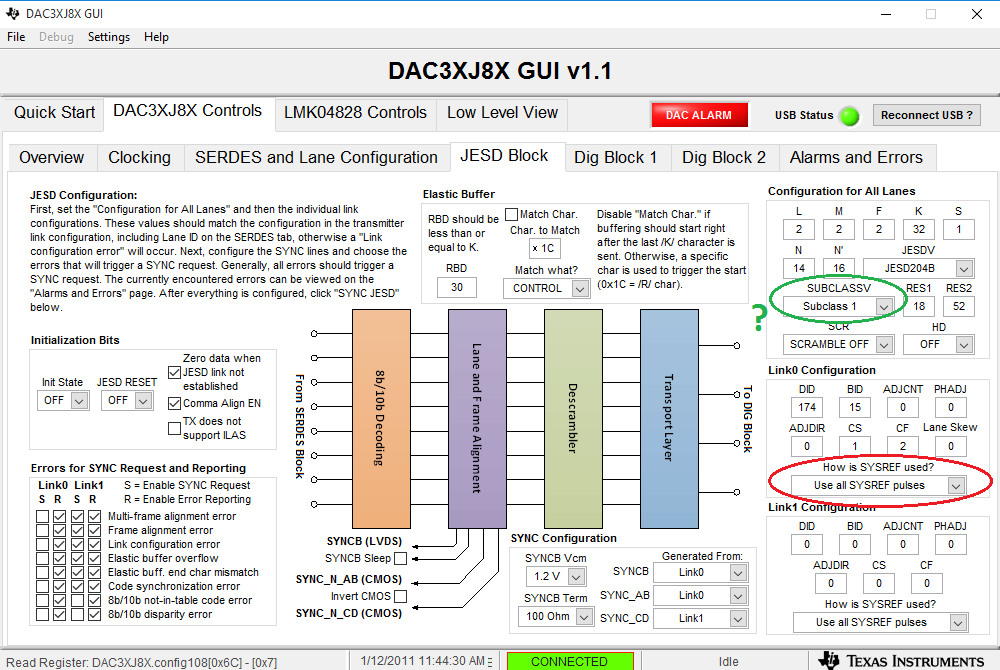

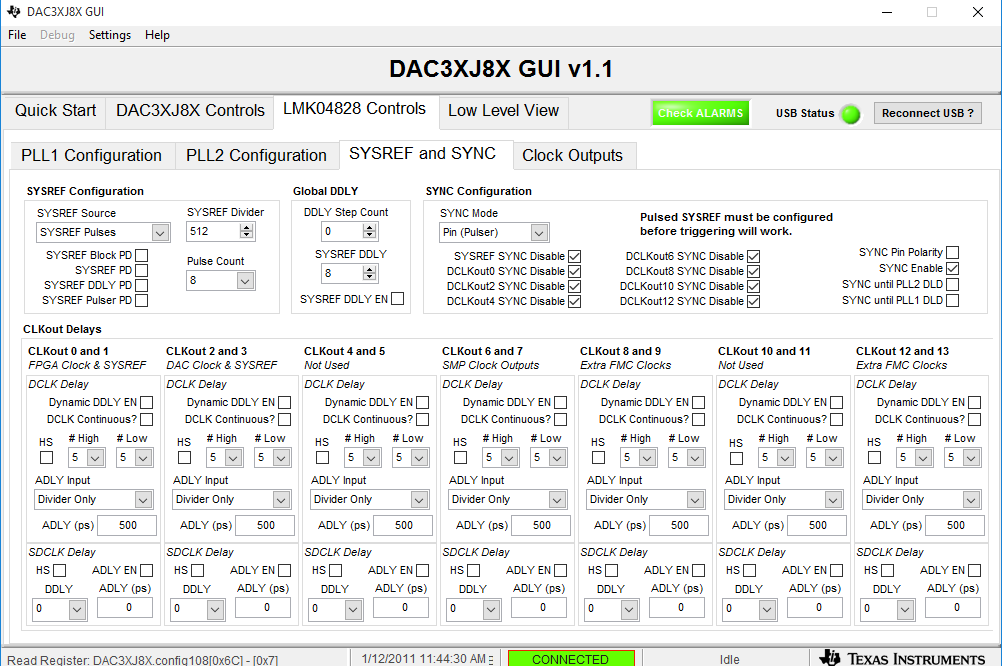

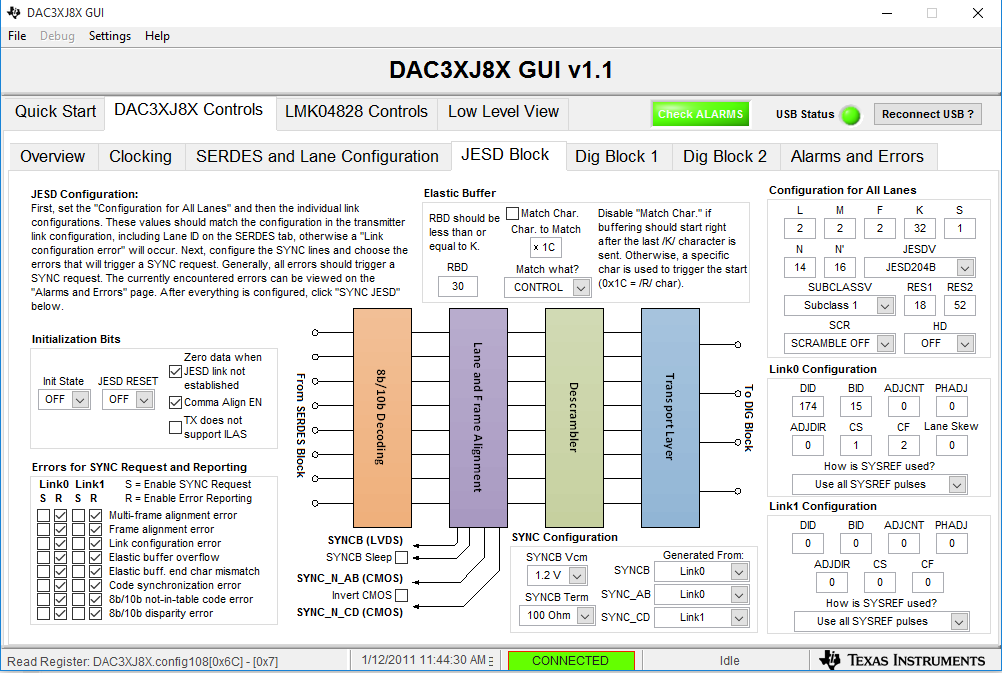

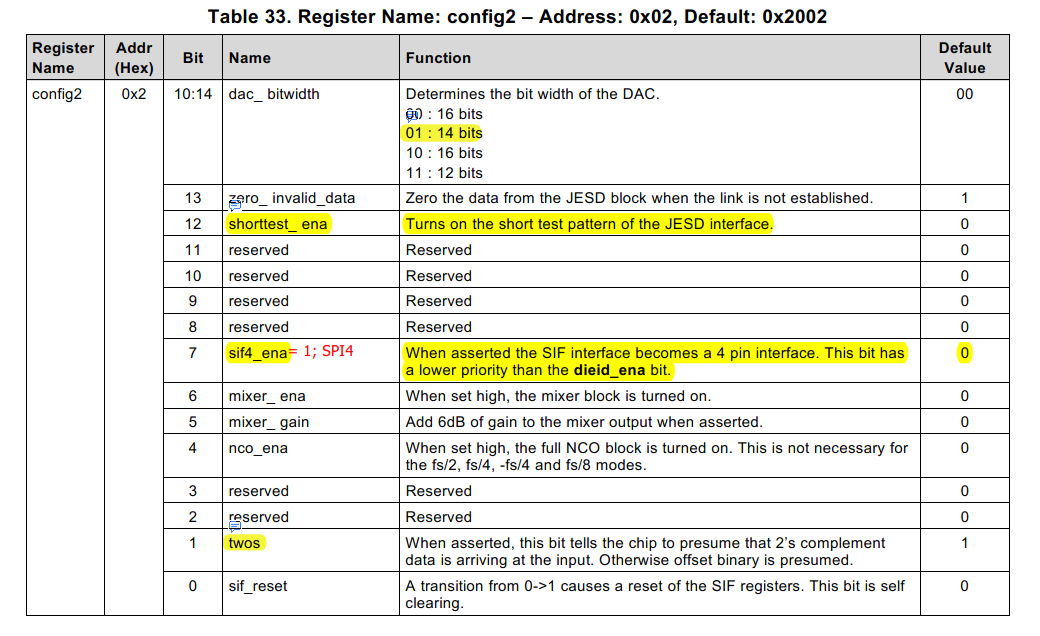

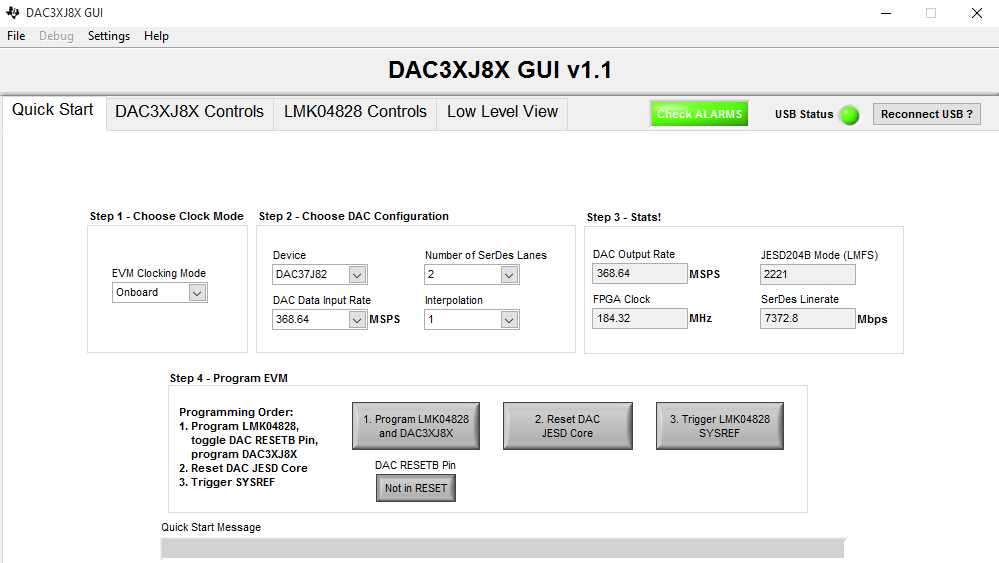

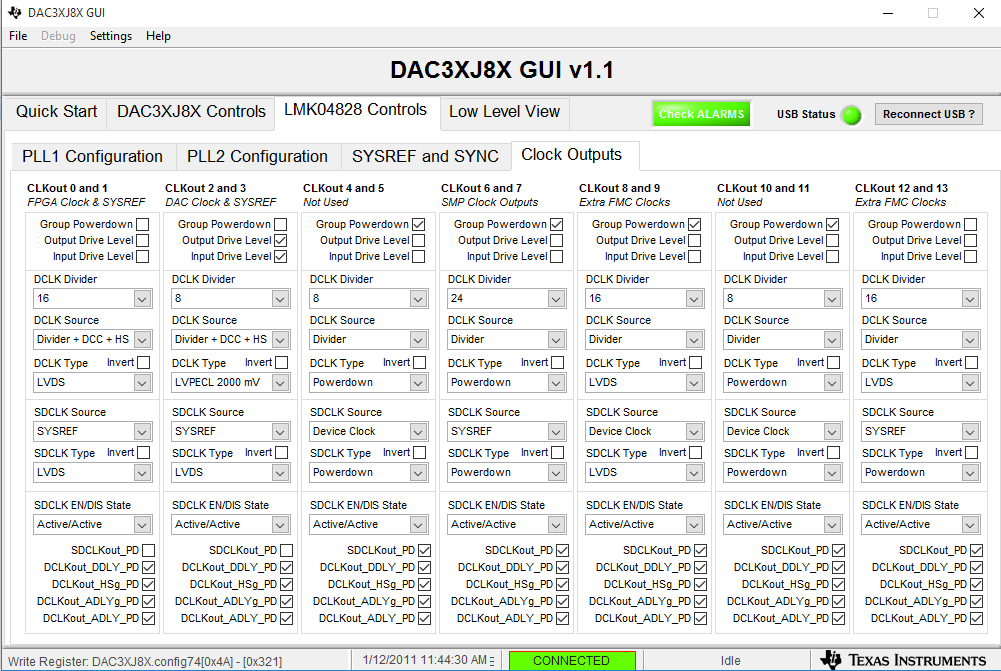

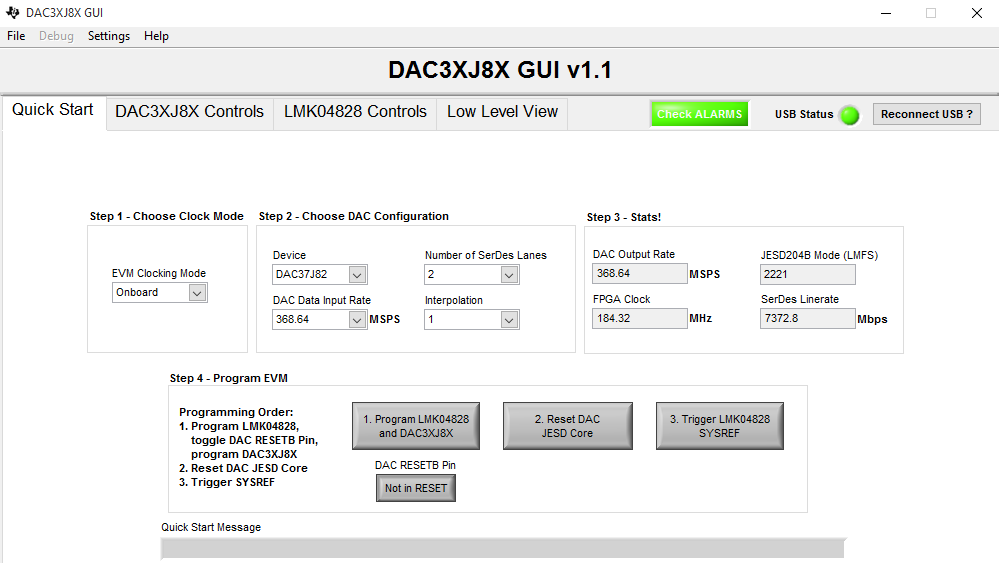

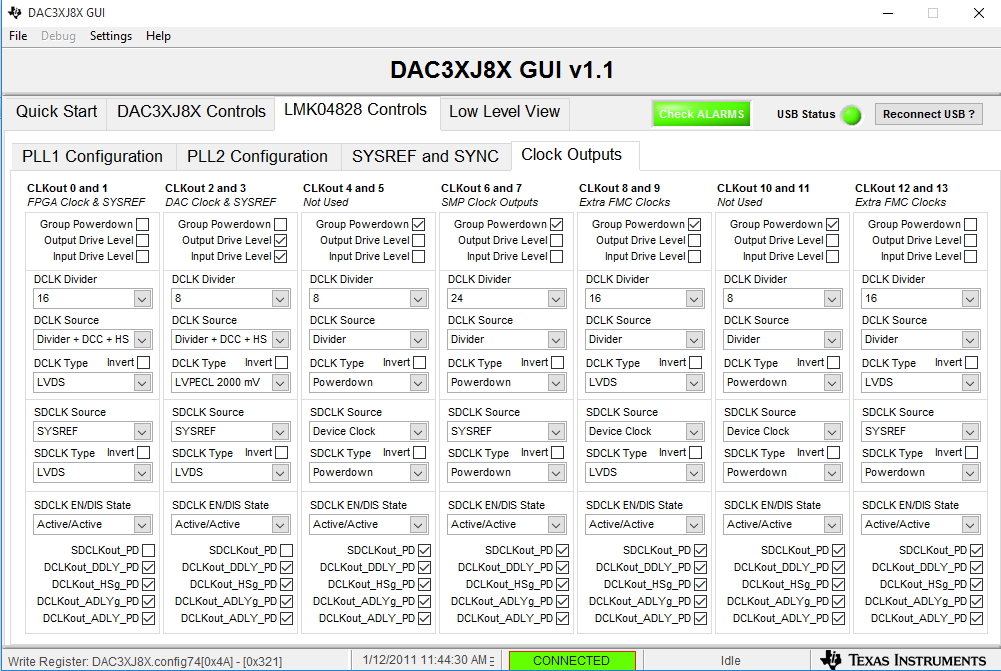

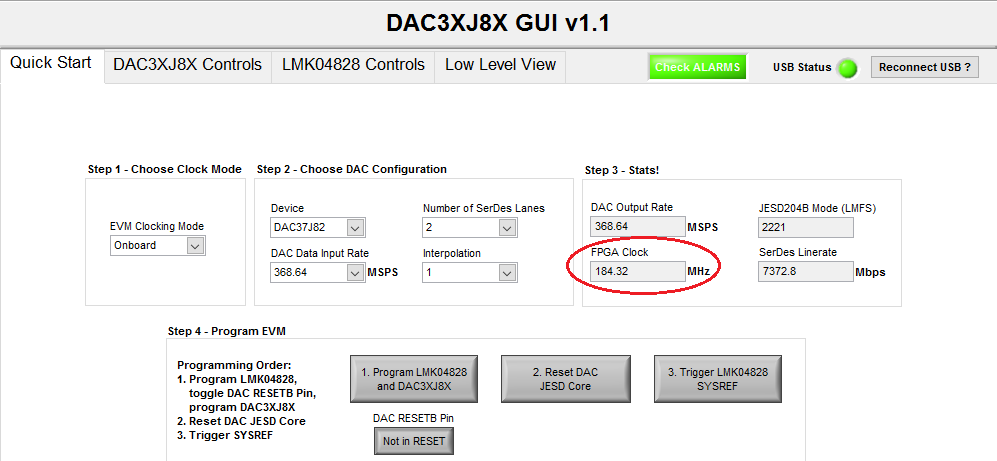

The DAC-configuration is as follows:

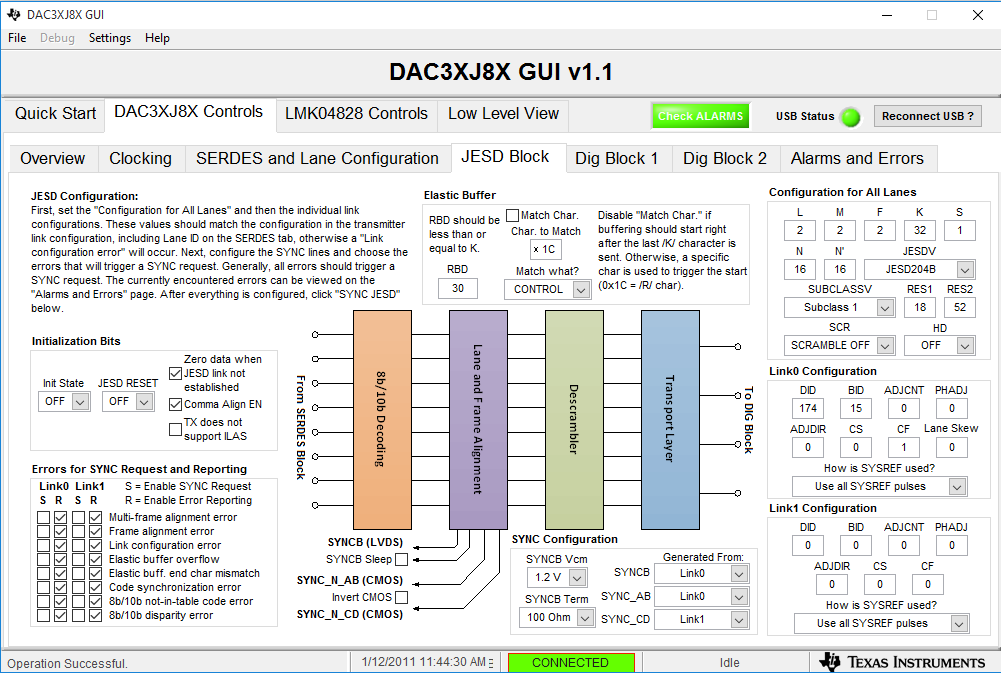

The JESD params are programmed with the same values as on the KC705:

See JESD-registers.txt, these are the JESD register settings on KC705:

--------------------------------------------

-- config 0

--

-- Default set always used on reset - F = 1, K = 32, Scrambling OFF

--

0 => x"8008", -- Addr x008 Rx Config 0

1 => x"0000", -- Data x0000_0001 Enable Lane Alignment

2 => x"0001",

3 => x"800C", -- Addr x00C Rx Config 0

4 => x"0000", -- Data x0000_0000 [0] Disable Scrambling

5 => x"0000",

6 => x"8020", -- Addr x020

7 => x"0000", -- Data x0000_0000 [7:0] F (octets per frame) = 1

8 => x"0000",

9 => x"8024", -- Addr x024

10 => x"0000", -- Data x0000_001F [4:0] K (Frames per multi) = 32

11 => x"001F",

12 => x"8014", -- Addr x014 Tx Only

13 => x"0000", -- Data x0000_0003 [7:0] ILA multiframes = 4

14 => x"0003",

15 => x"880C", -- Addr x80C Tx Only

16 => x"0000", -- Data x0000_0FAE [15:12] BID = xF [7:0] DID = xAE

17 => x"0FAE", --

18 => x"8810", -- Addr x810

19 => x"0010", -- Data x0010_1002 [25:24] CS=0 [20:16] N' = x10 [12:8] N = x10 [7:0] N = x2

20 => x"1002", --

21 => x"8814", -- Addr x814

22 => x"0401", -- Data x0401_0100 [28:24] CF [16] HD [12:8] S

23 => x"0100",

24 => x"8818", -- Addr x818 Tx Only

25 => x"0000", -- Data x0000_1234 [7:0] RES1 [15:8] RES2

26 => x"1234",

27 => x"0000",

See DAC37J82_Settings.cfg, these are the DAC register settings:

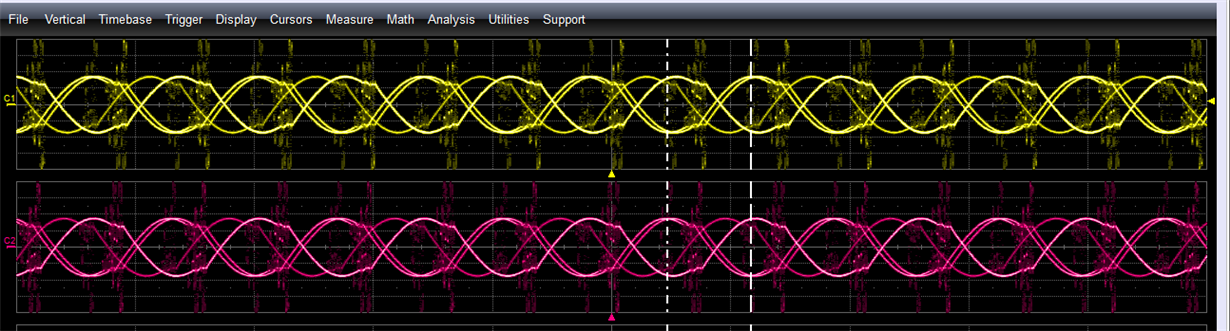

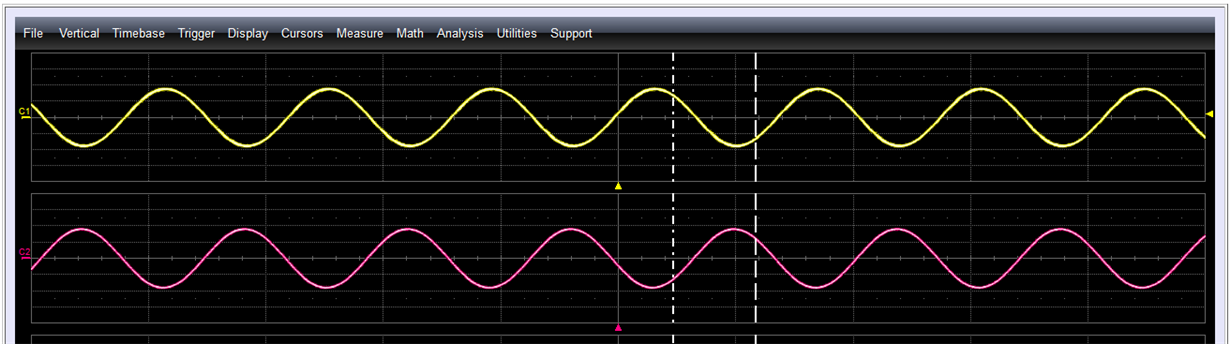

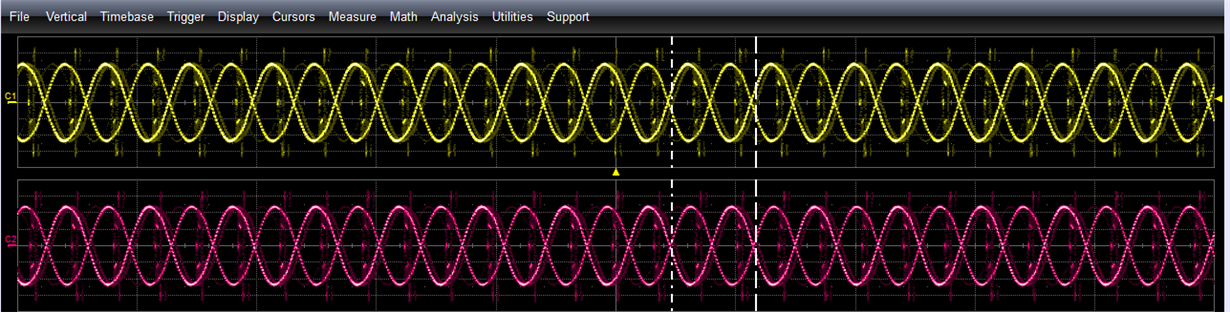

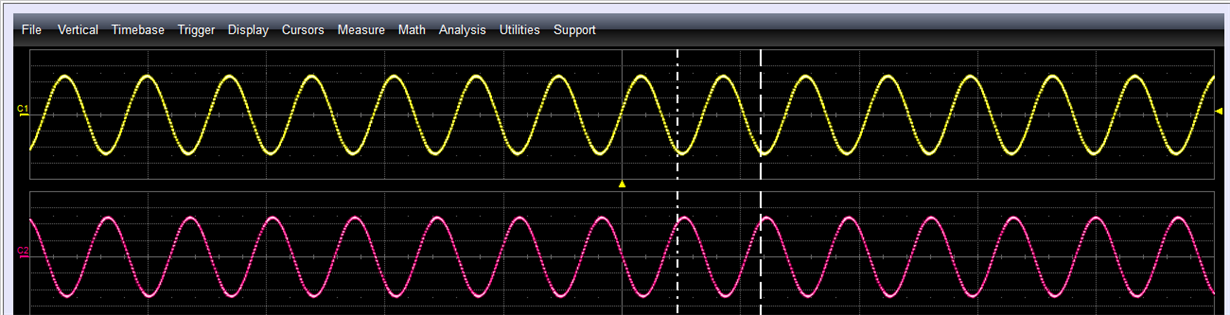

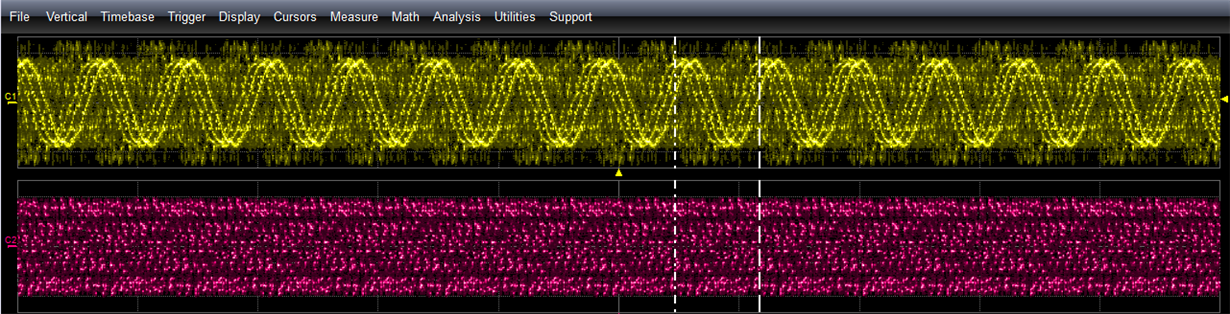

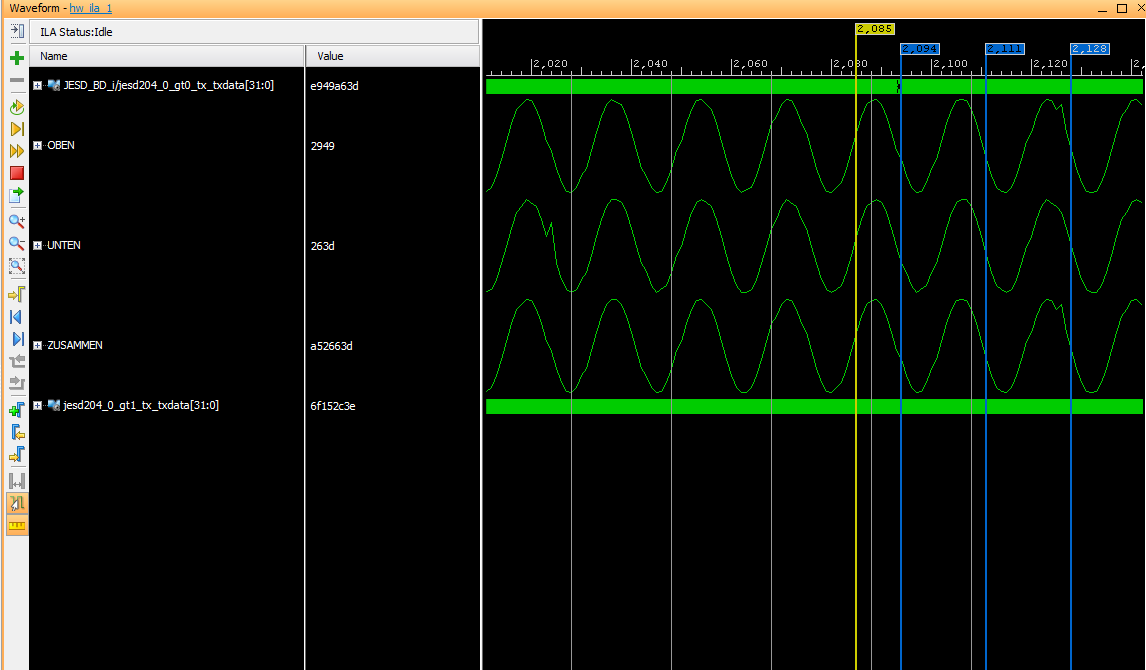

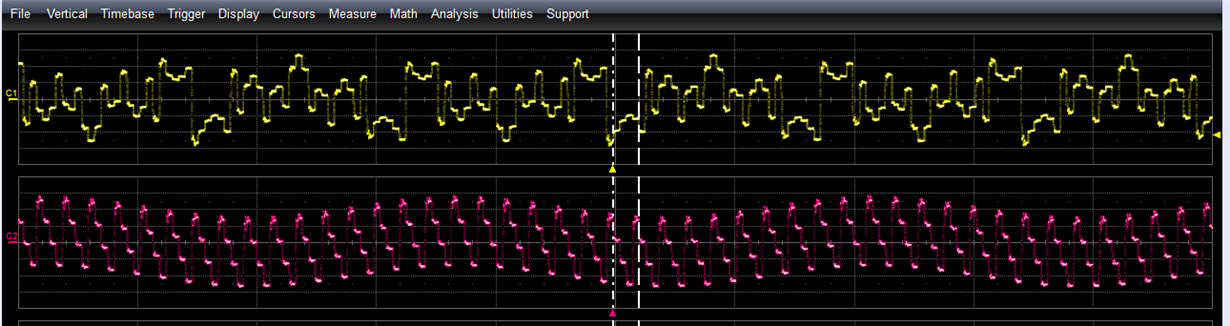

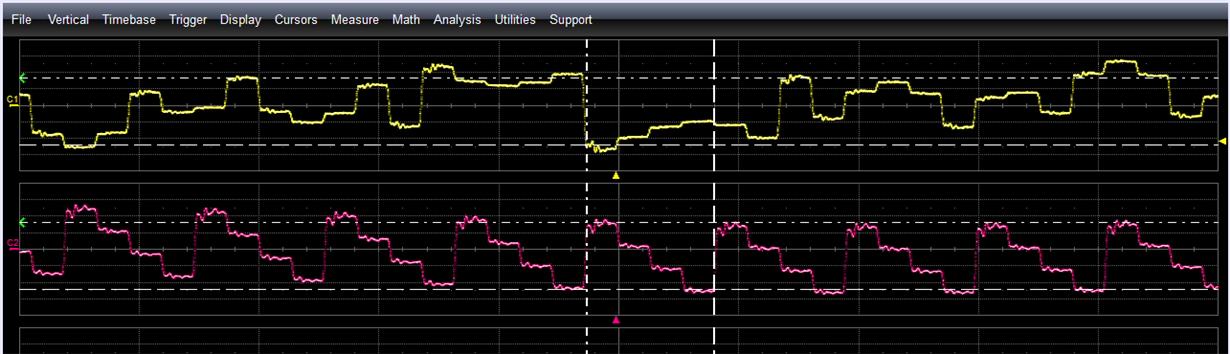

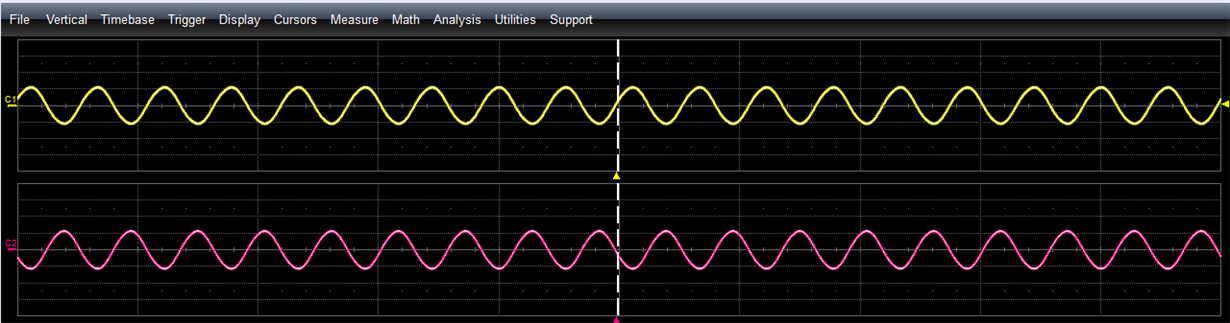

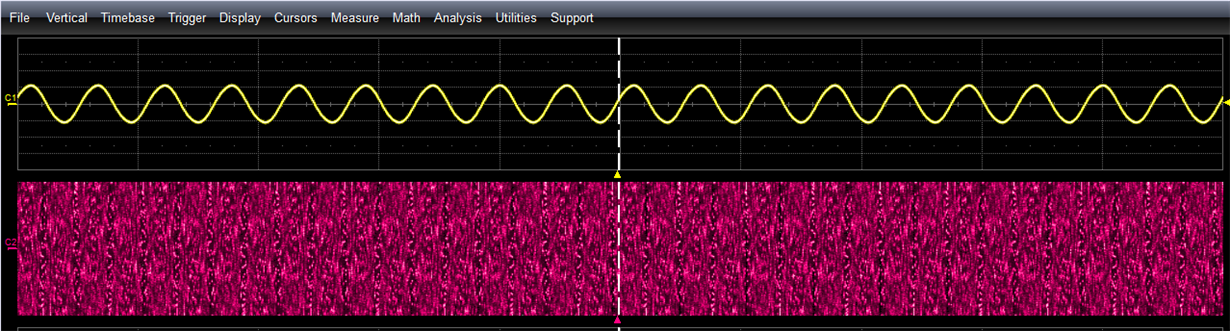

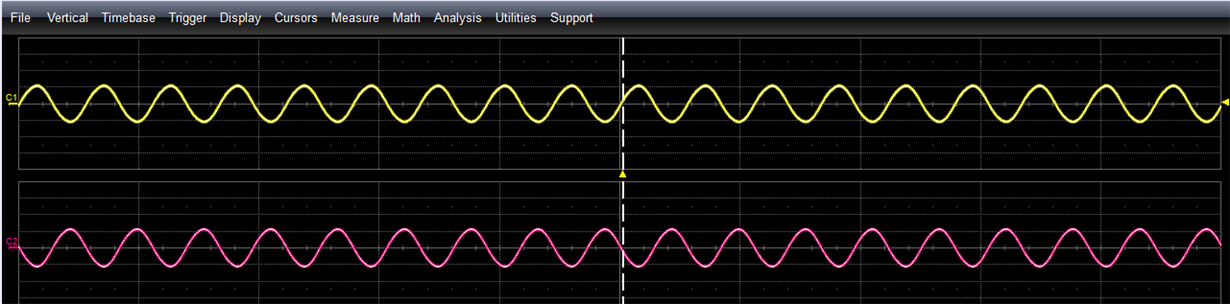

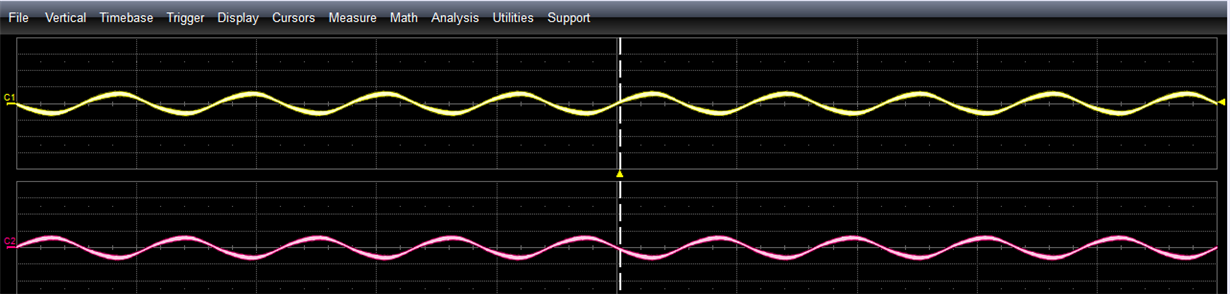

The sine wave output on the analog lanes looks as follows:

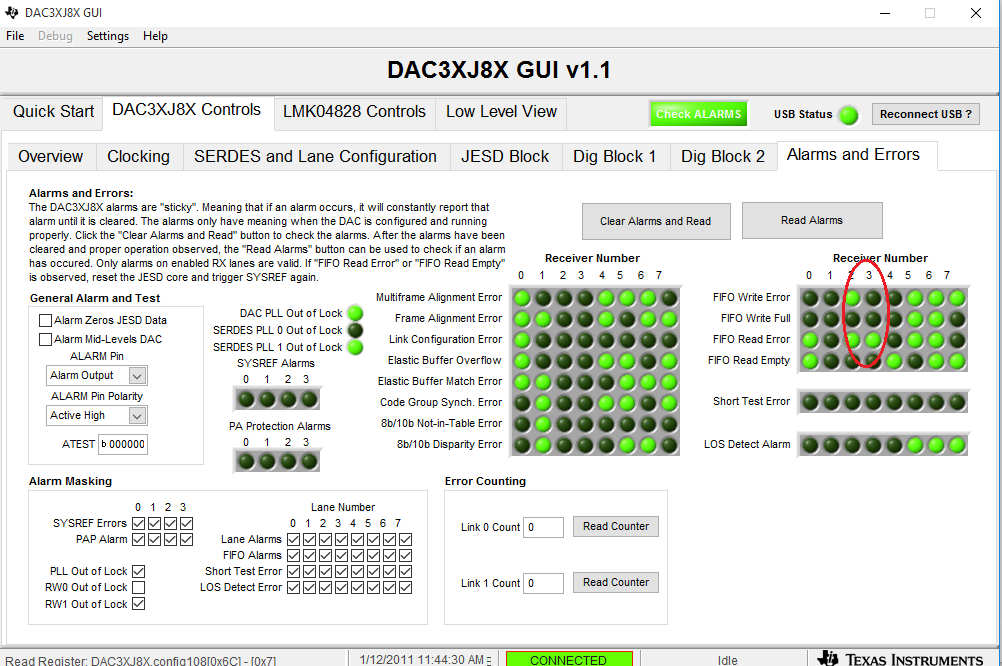

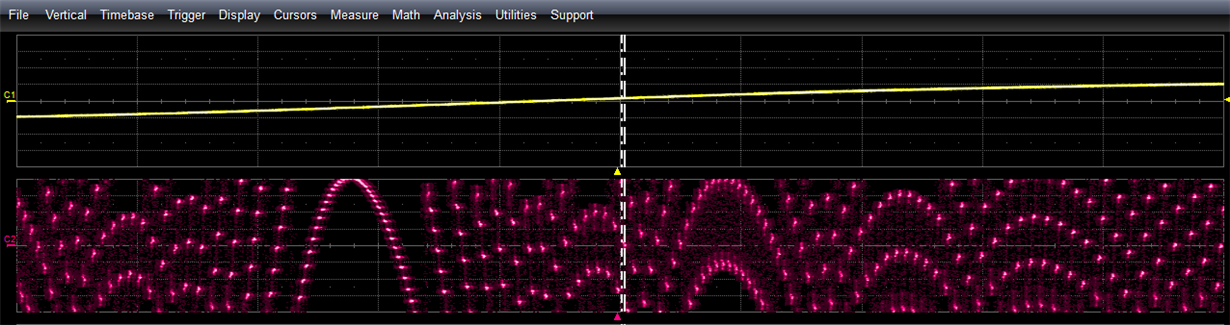

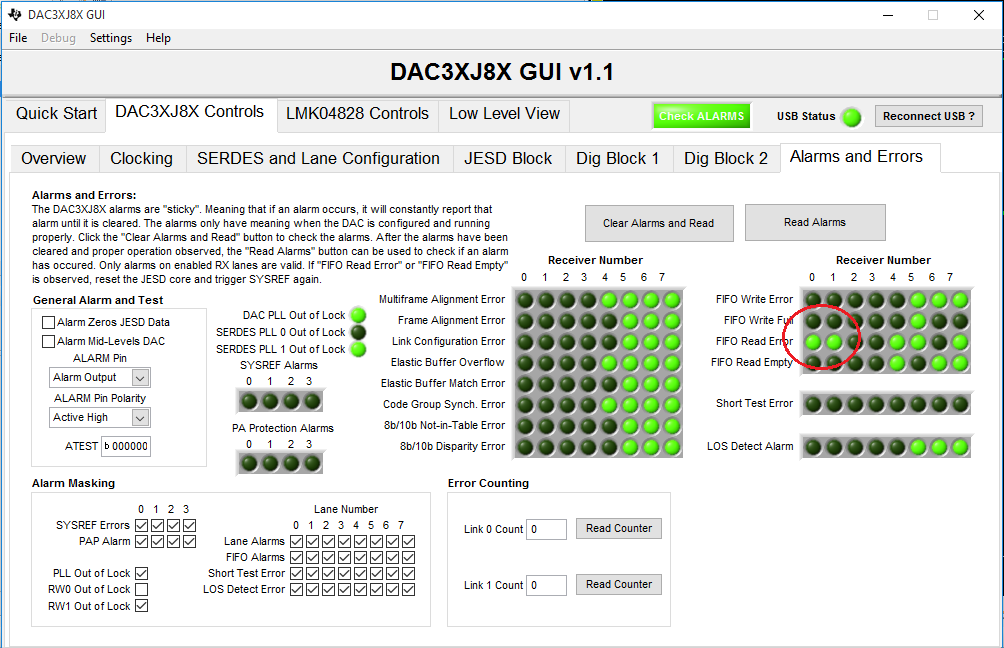

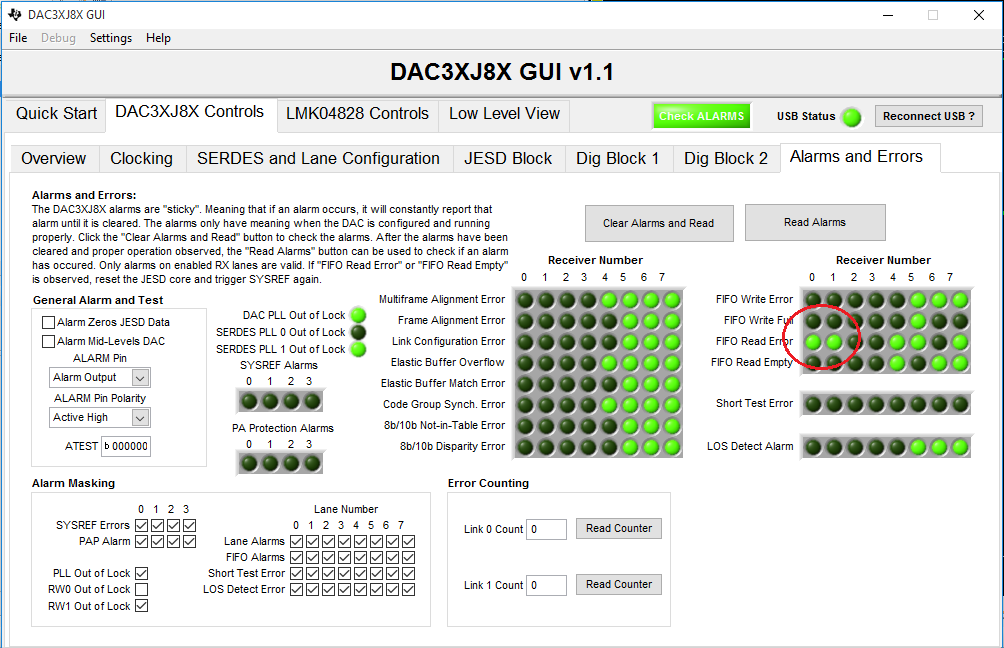

DAC alarms are as follows:

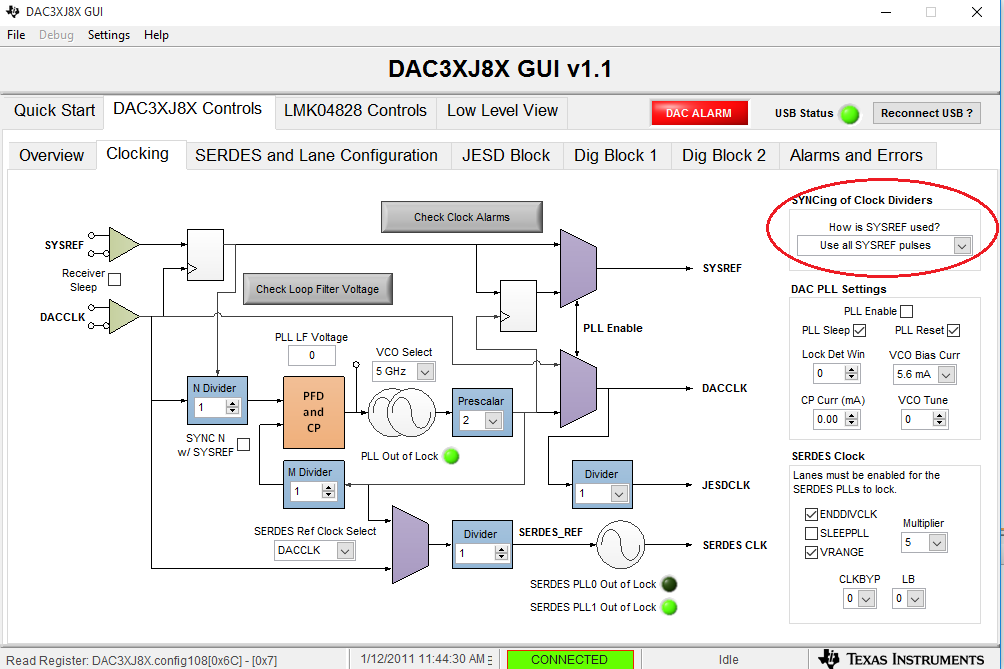

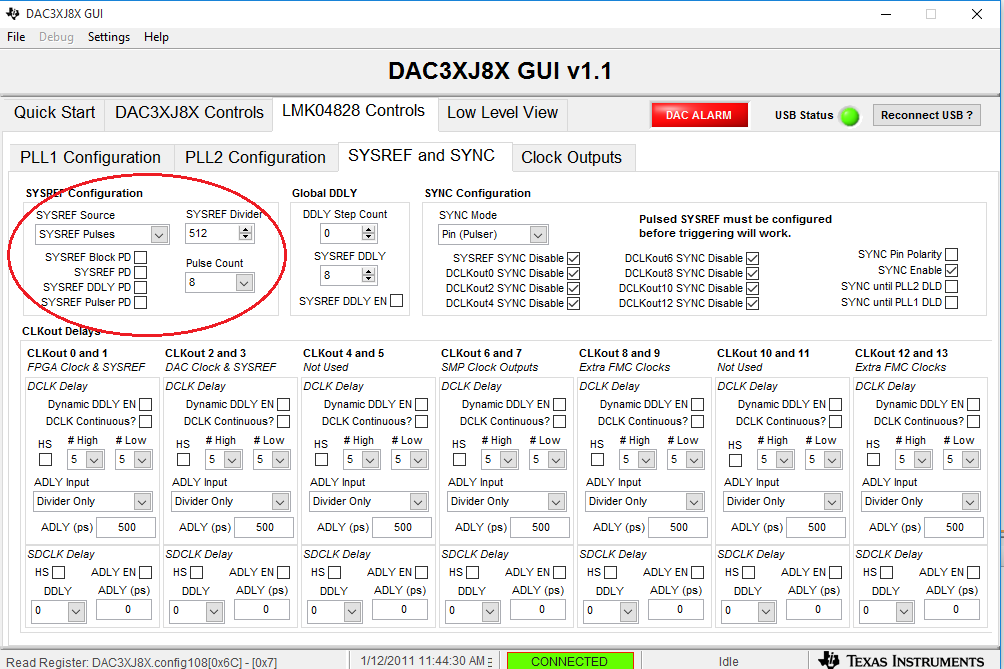

It seems to be a synchronisation error, but I'm struggling with the reason how this can happen. Clocks to the FPGA REFCLK = 184.32 and Core clock = 92.12 are correct, FPGA is in SYNC. Is there a specific DAC startup-sequence in addition to RESET DAC JESD-Core and Trigger SYSREF ?

Please take a look to the DAC register config and JESD config: do you see any mismatch ?

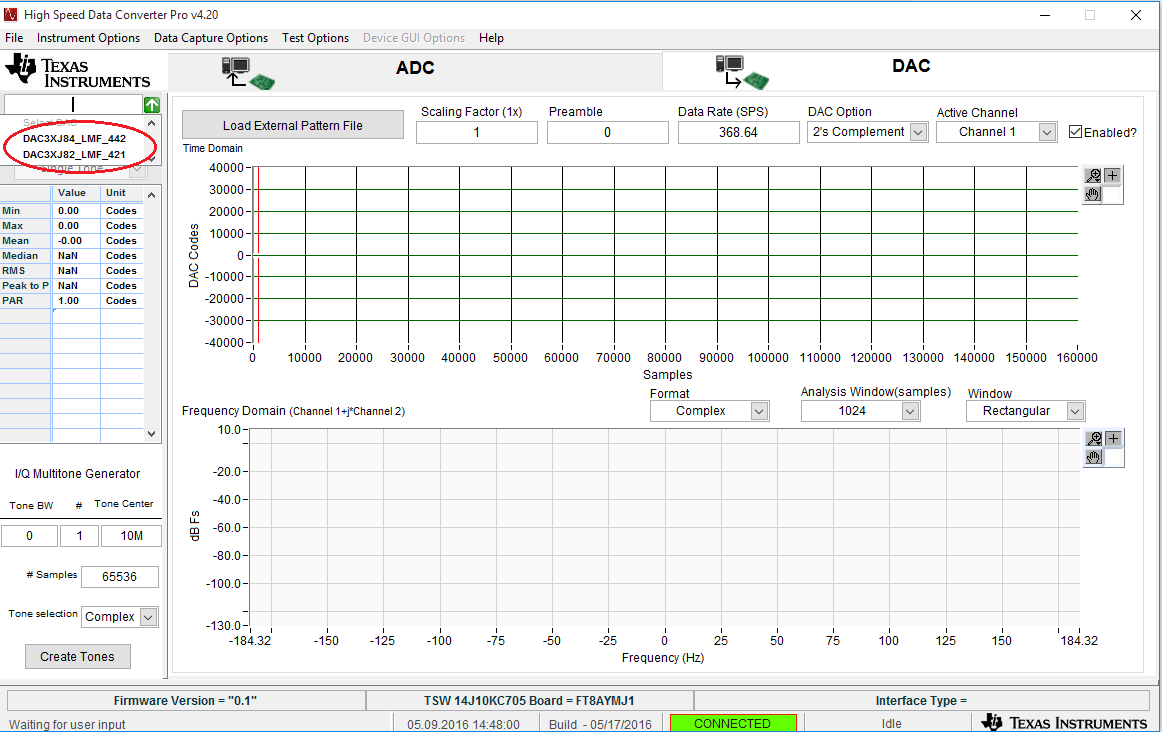

In addition to this problem, we do not see any correct analog output using the http://www.ti.com/lit/zip/slac690 Xilinx firmware or downloading firmware to KC705 as described in SLAU580A and SLAU547B.

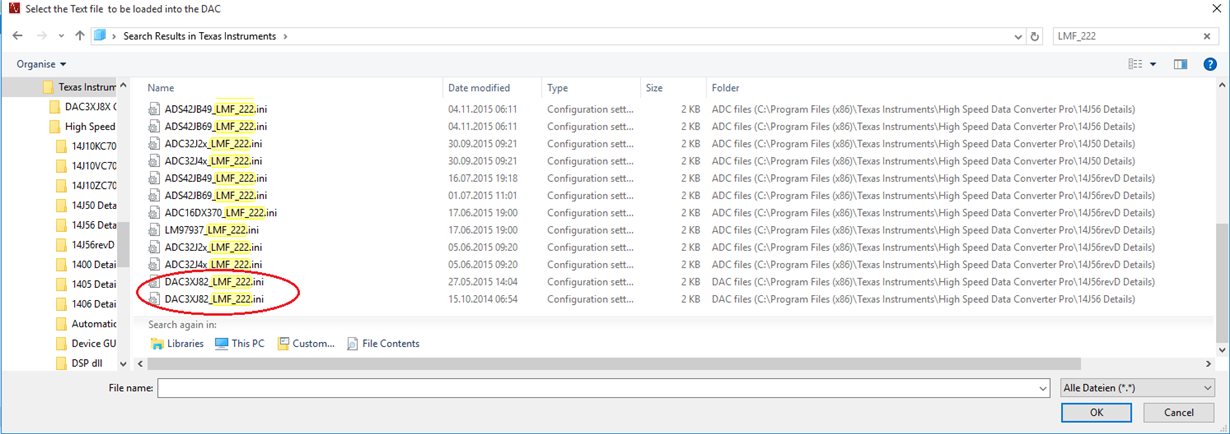

Please, could you send me a DAC37J82 config file which has the correct DAC settings to interconnect with the http://www.ti.com/lit/zip/slac690 Xilinx firmware.

Thanks in advance.

Regards,

Zoltan Gergely