Hi everyone,

I'm using ADC12J4000EVM to interface with our FPGA board.

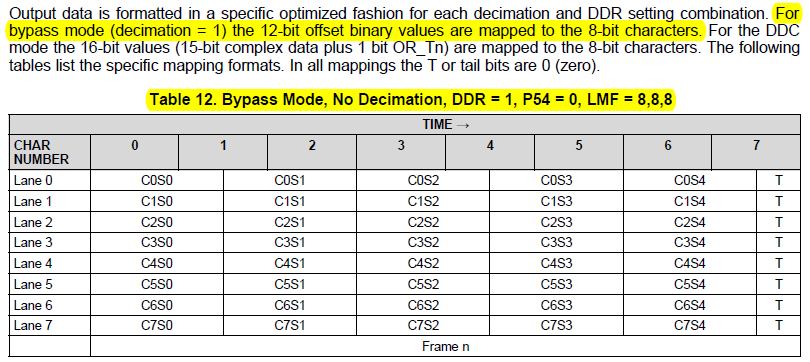

I read the datasheet of ADC12J4000, and I noticed that on page 40 it says:"For bypass mode (decimation = 1) the 12-bit offset binary values are mapped to the 8-bit characters."

I didn't understand how 12-bit could be mapped to 8-bit without loss of information, and I cannot find more detailed explanation of this. Can anyone explain it to me?

I want to get the 12-bit raw ADC data from the FPGA board. How can I recover 12-bit offset binary data from the 8-bit characters?

Thank you very much.

Regards,

Tong