Other Parts Discussed in Thread: ADS52J90, LMK04826

Hello support team,

Our customer is now evaluating JESD204B communications using ADS52J90EVM.

The customer varies the frequency of SYSREF_SERDES signals.

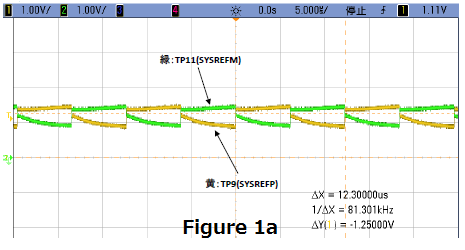

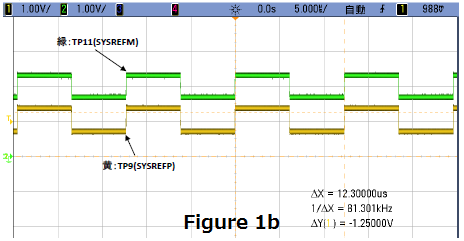

When the frequency of the SYSREF_SERDES signals input to ADS52J90 is lowered, the waveform of LVDS signals will become dull as shown in Figure 1a or the they will be in-phase as shown in Figure 1b.

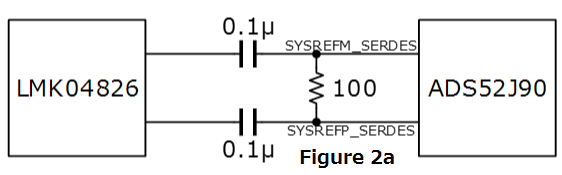

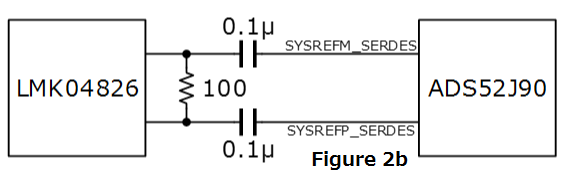

When the terminating resistor is changed from behind AC coupling capacitors (Figure 2a) to before them (Figure 2b), the waveform of LVDS signals will be normal.

Here's a question.

1. As shown in Figure 2a, why does the waveform become dull or in-phase when the terminating resistor is placed behind the AC coupling capacitors ?

2. As in Figure 2b, is there any problem when the terminating resistor is placed before AC coupling capacitors?

Please teach me.

Best regards,

M. Tachibana