Part Number: TSW4806EVM

I have a customer having issues in getting the TSW4806EVM to produce a 100MHz clock. Here is the explanation that he gave:

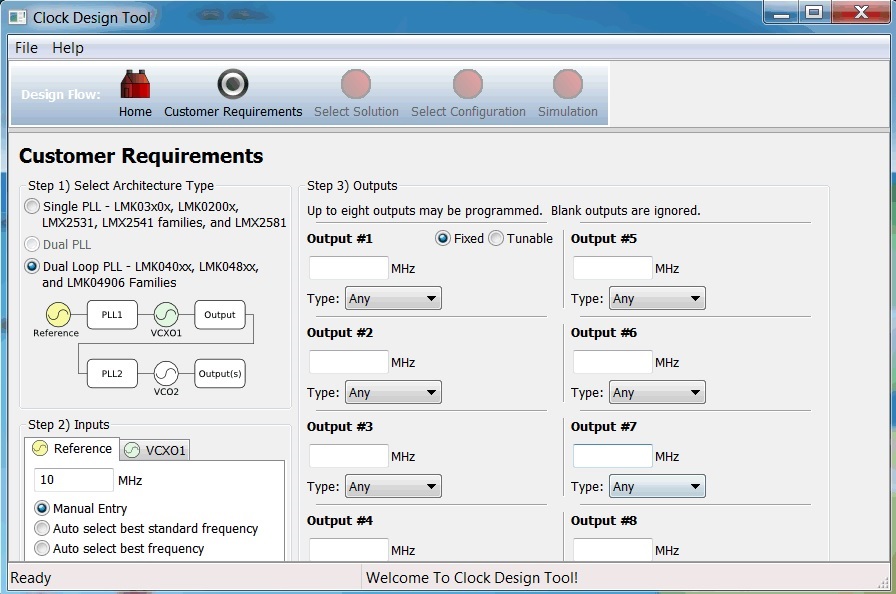

I am doing everything I can to get the module generate a 300MHz and 100MHz clock using TSW4806 EVM board.

Instead, I got 303MHz and 101MHz, respectively and each clock has a fairly large jitter that varies from 298MHZ to 305MHz as a min. and max. repetitive rate.

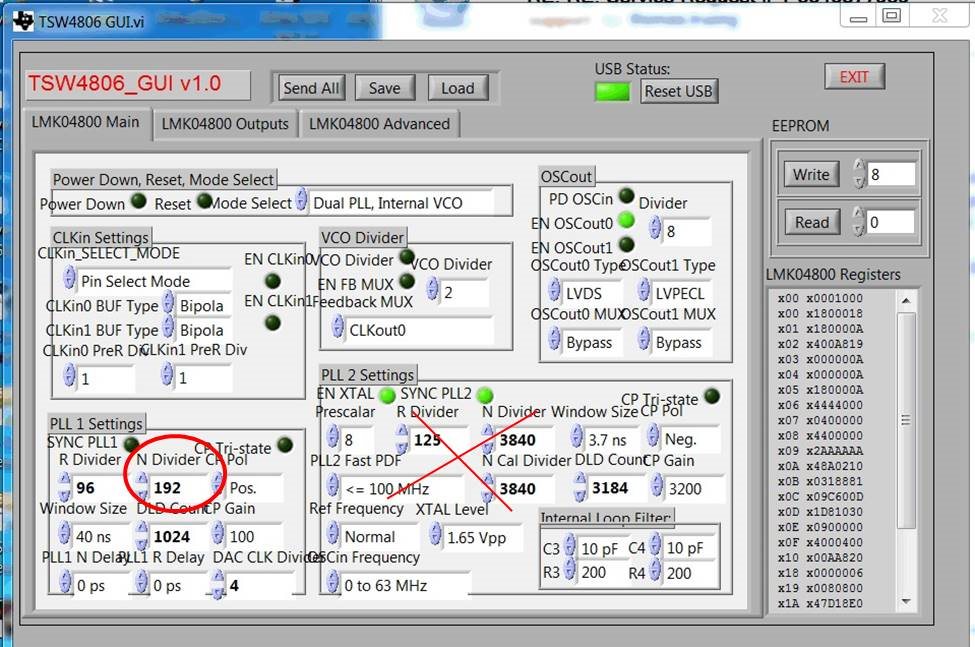

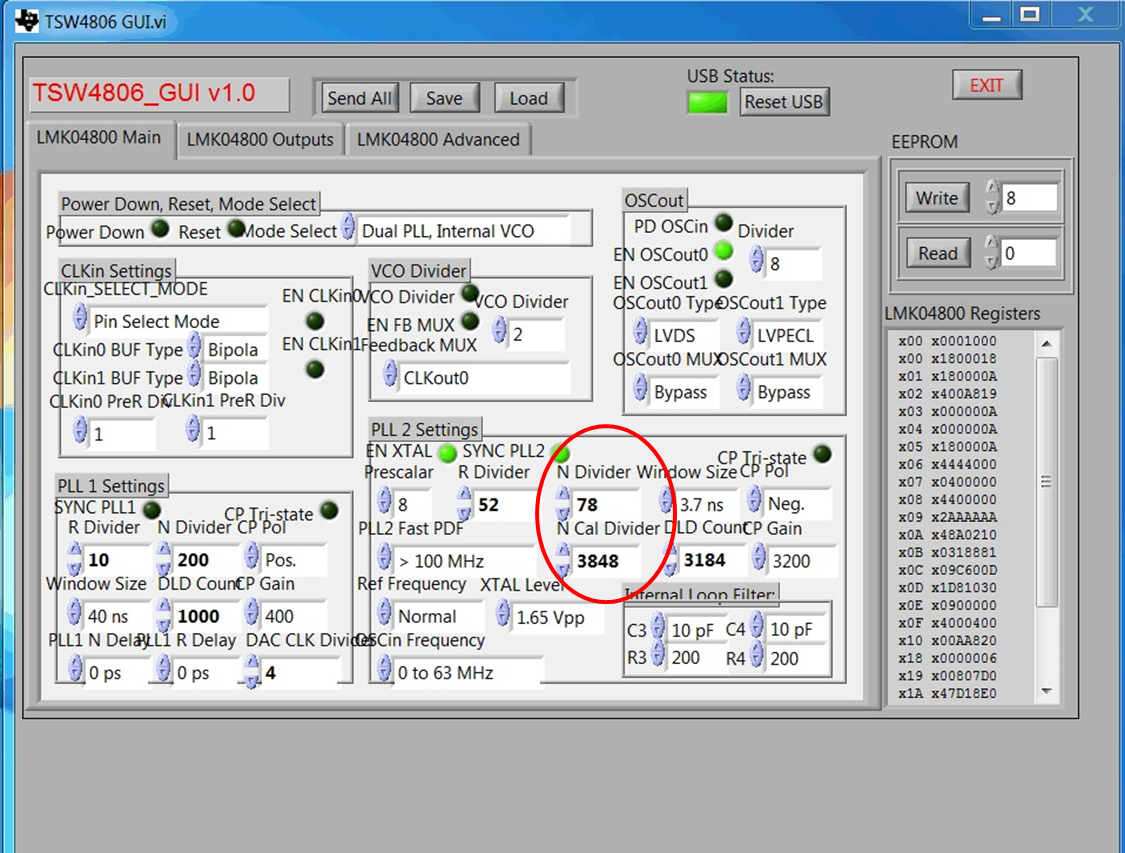

Y2 VCXO is installed for PLL2. Captured configuration used shown as below.

I have included a document which shows the setting that he is using.

TSW4806EVM Frequency Issue.docx

It almost sounds like this is unstable. Can you look at the setting and see if the customer is doing anything wrong?

Thanks for your help with this!

Richard Elmquist