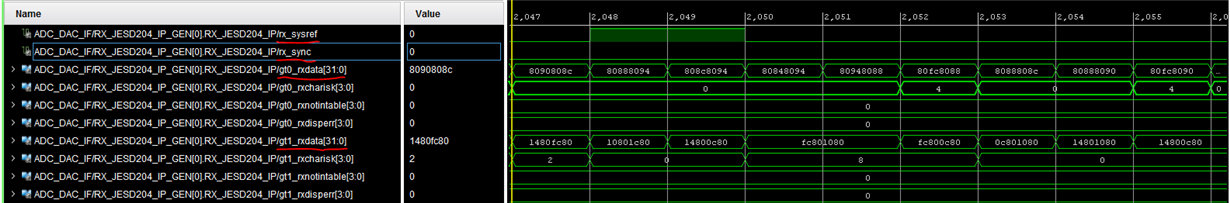

As the title states I'm having trouble getting the ADC to step through the JESD204 initialization sequence. This is with the eval board connected to a Xilinx KCU116 Ultrascale+ demo board via the FMC connector. What I observe is the ADC not sending /K/ characters when the FPGA asserts sync~. I instead see a characters similar to the following with no pattern to them :

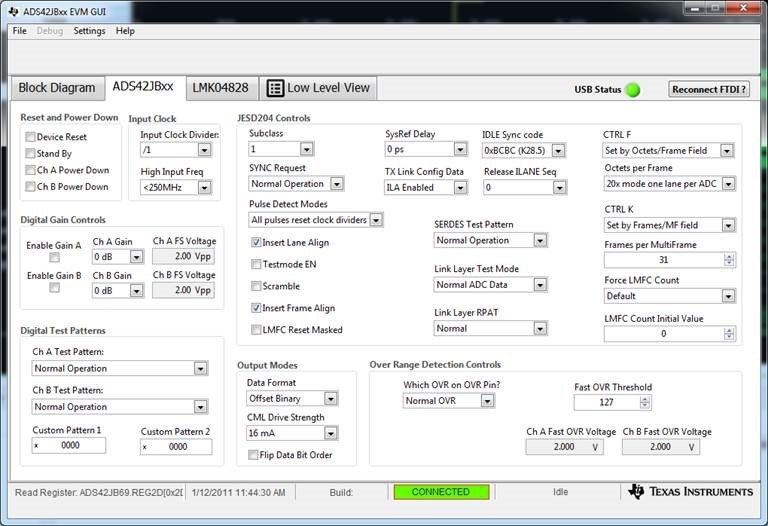

When I set the ADC to send a continuous stream of /K/ characters, the FPGA deasserts sync~ and completes the code group sync phase. When switching back to normal ADC data, the FPGA asserts sync~ again but I don’t see the code group sync or the initial lane alignment sequence in the data coming across. A few important settings that I’m using are :

100 MHz ADC clock

200 MHz FPGA device clock

2 Gbps line rate

LMFK = 2, 2, 2, 32

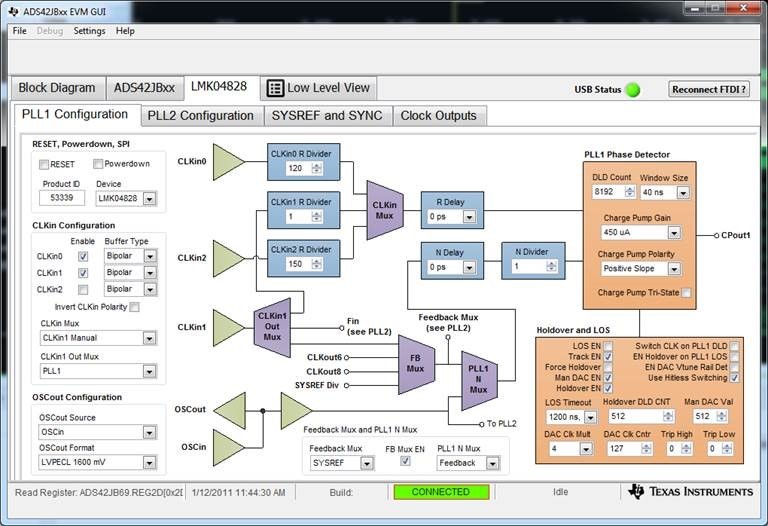

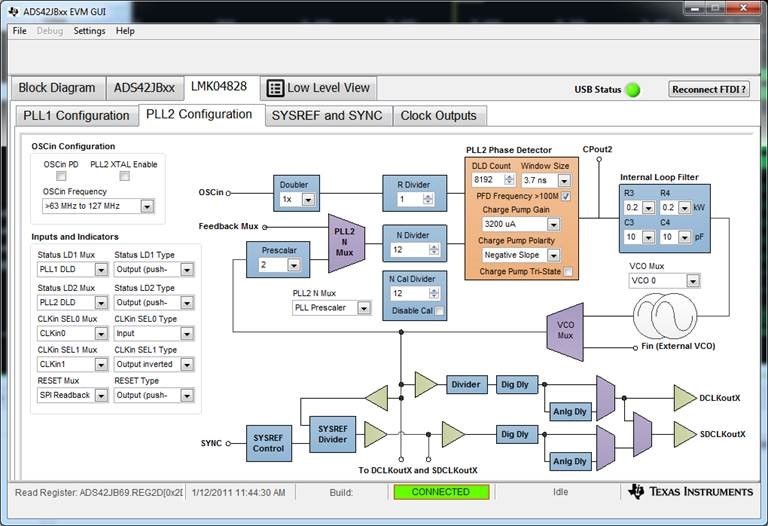

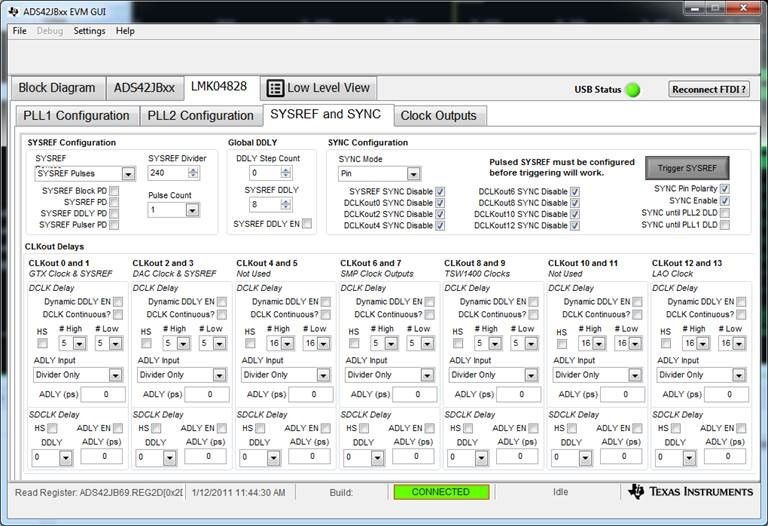

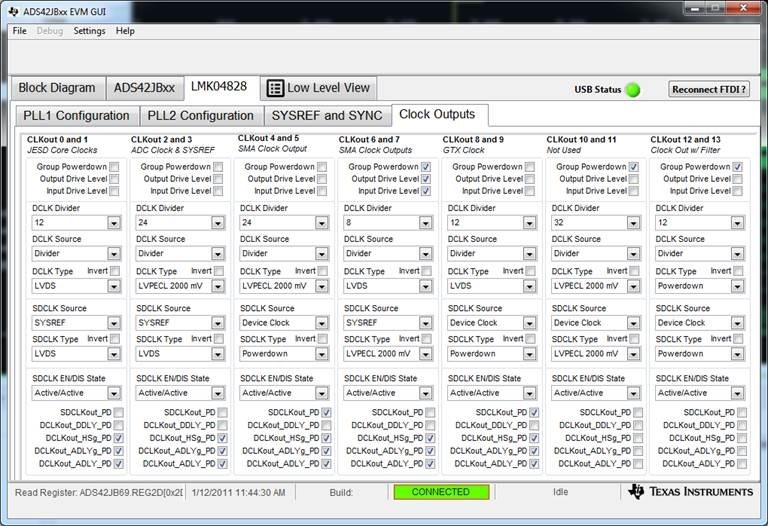

Is there anything obvious that stands out as causing the issue here? For reference, the settings that I’m using in the EVM GUI are below :

Thank you