Other Parts Discussed in Thread: ADC12J4000EVM, ADC12J4000, LMK04828

Is it possible to use an external trigger with the TSW14J57EVM connected to the ADC12J4000EVM? Has this feature been implement yet?

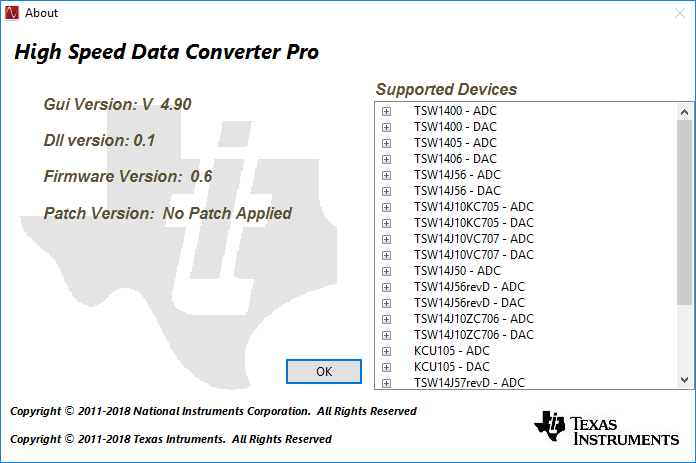

Some other forum posts from awhile back seem to indicate that the firmware does not have external trigger support on the newer TSW14J57EVM (https://e2e.ti.com/support/data_converters/high_speed_data_converters/f/68/t/620008?tisearch=e2e-sitesearch&keymatch=TSW14J57EVM%20trigger