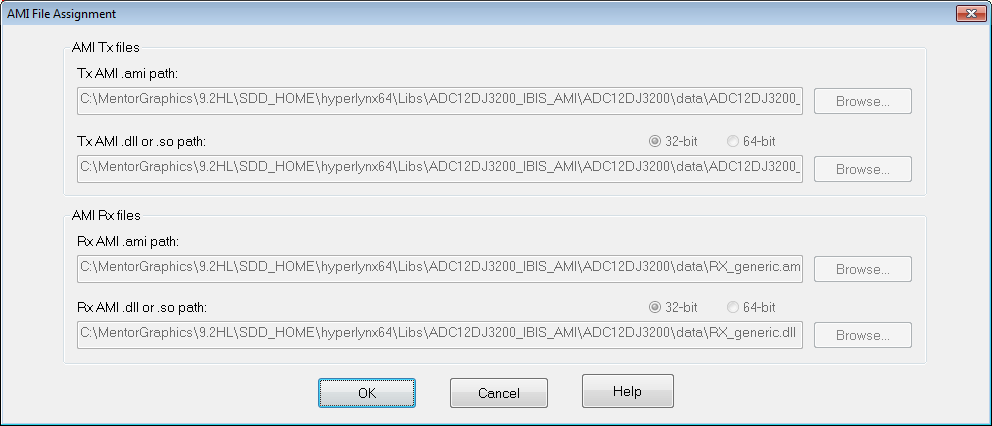

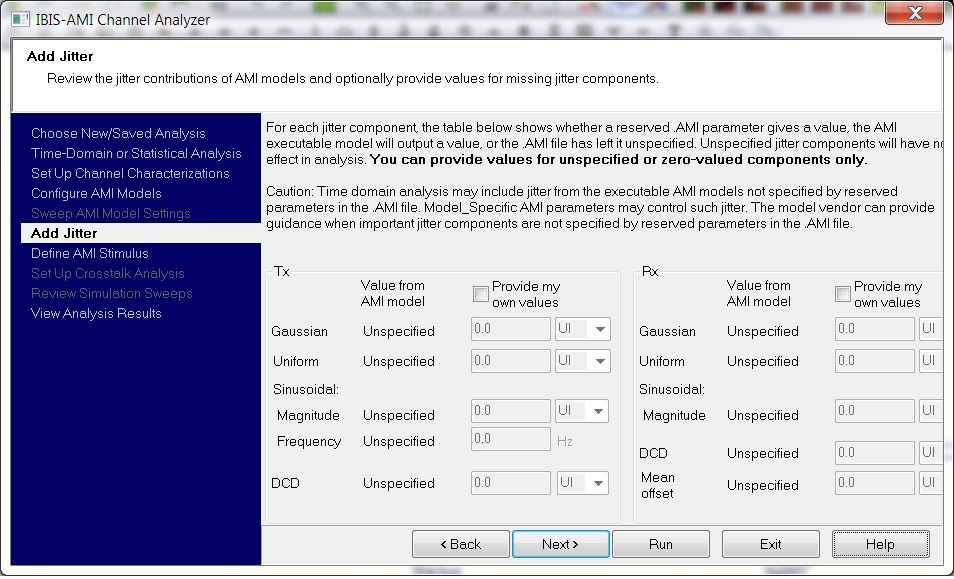

I am interfacing ''ADC12DJ3200AAV'' ADC with FPGA. I have started SI simulation for this.

While assigning ibis model to ADC, all the DA & DB lines are in input direction only in hyperlynx tool. It should be output at any time. But i am unable to change the direction as the default direction for this pins are only INPUT. Please help me on this, Is there any issue with ibis model or any other issue?

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.