Hello,

We are trying to generate the SPI input for the DAC from an FPGA board.

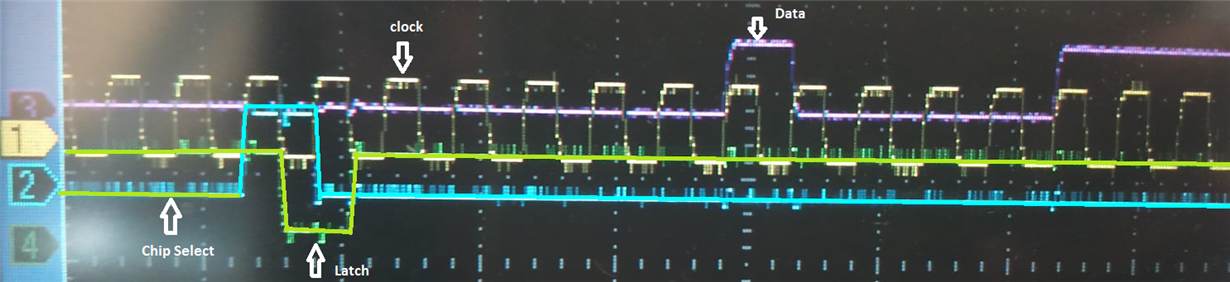

So far we have tested our waveform against the Clock. (SCLK)

SCLK has 10MHz Frequency. The address of the SPI register is 0100, the data we are sending is "111111111111".

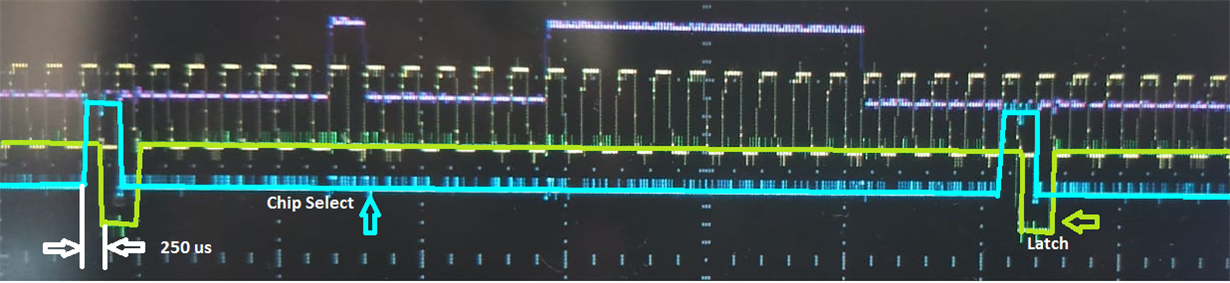

The Chip select goes high for one clock cycle after 24 bits are sent and Latch goes low when Chip select goes high.

But we are not able to see any output from the DAC outputs.

Is there any other thing that should be taken care of?

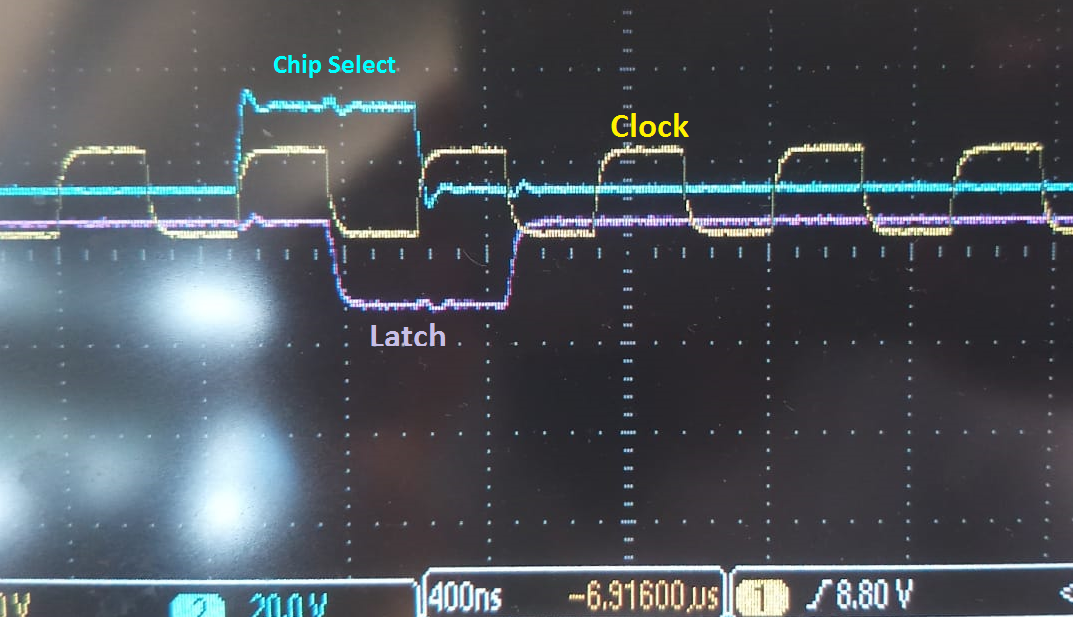

When we plot the waveform that are going to the DAC chip in MATLAB, we can see that the setup time is negative (i.e. Data comes a little later than the rising edge of the clock)

Also, how can I make sure that the setup and hold time requirements are met in the Inputs.