Other Parts Discussed in Thread: LMK04828

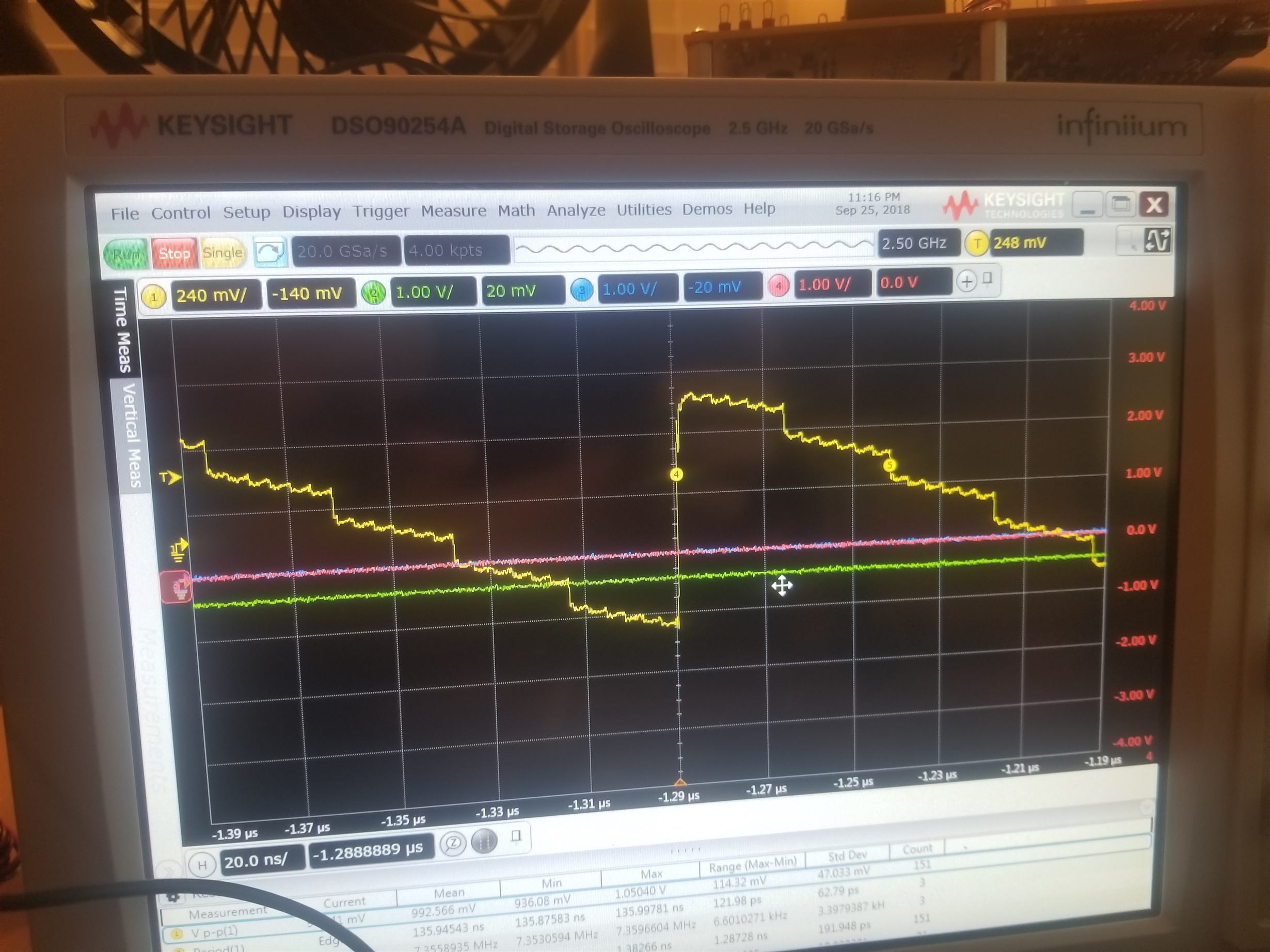

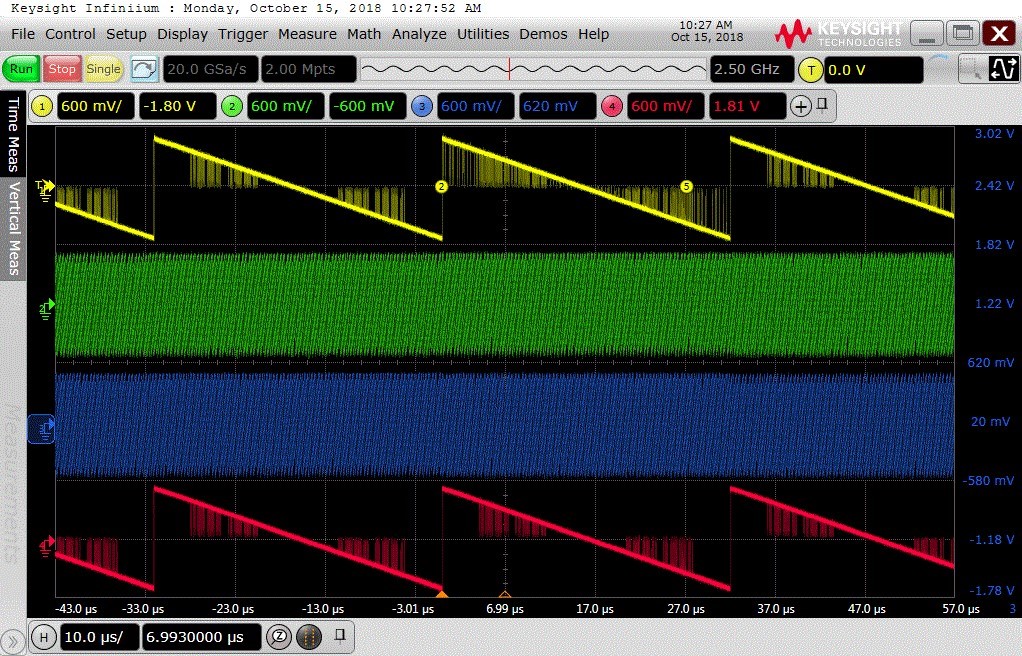

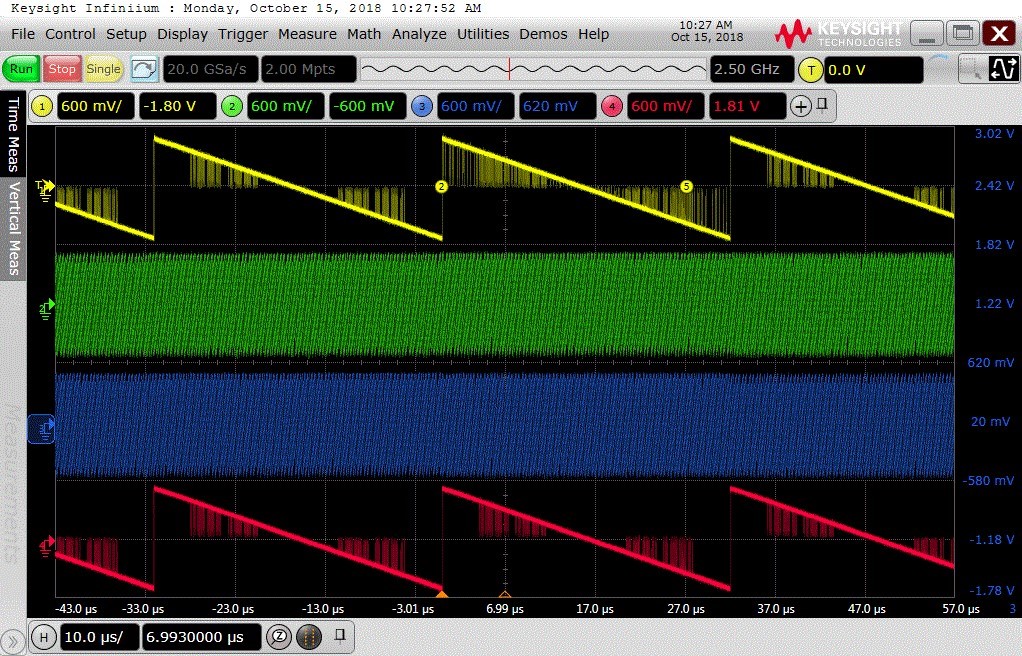

I am seeing the SYNC signal go high, and it looks like the link is progressing past ILA to data, but I'm not seeing anything out of the DAC39J84 consistently.

Here is a dump of the registers in the DAC (in decimal, high byte then low-bye format)

DAC Config Regs:

Config Reg 0

[0, 24]

Config Reg 1

[0, 80]

Config Reg 2

[32, 130]

Config Reg 3

[163, 1]

Config Reg 4

[0, 0]

Config Reg 5

[255, 3]

Config Reg 6

[255, 255]

Config Reg 7

[66, 4]

Config Reg 8

[0, 0]

Config Reg 9

[0, 0]

Config Reg 10

[0, 0]

Config Reg 11

[0, 0]

Config Reg 12

[4, 0]

Config Reg 13

[4, 0]

Config Reg 14

[4, 0]

Config Reg 15

[4, 0]

Config Reg 16

[0, 0]

Config Reg 17

[0, 0]

Config Reg 18

[0, 0]

Config Reg 19

[0, 0]

Config Reg 20

[0, 0]

Config Reg 21

[0, 0]

Config Reg 22

[0, 0]

Config Reg 23

[0, 0]

Config Reg 24

[0, 0]

Config Reg 25

[0, 0]

Config Reg 26

[0, 0]

Config Reg 27

[0, 0]

Config Reg 28

[0, 0]

Config Reg 29

[0, 0]

Config Reg 30

[68, 68]

Config Reg 31

[68, 64]

Config Reg 32

[64, 68]

Config Reg 33

[0, 0]

Config Reg 34

[27, 27]

Config Reg 35

[255, 255]

Config Reg 36

[0, 32]

Config Reg 37

[32, 0]

Config Reg 38

[0, 0]

Config Reg 39

[0, 0]

Config Reg 40

[0, 3]

Config Reg 41

[255, 255]

Config Reg 42

[0, 0]

Config Reg 43

[0, 0]

Config Reg 44

[0, 0]

Config Reg 45

[0, 0]

Config Reg 46

[255, 255]

Config Reg 47

[0, 4]

Config Reg 48

[0, 0]

Config Reg 49

[16, 1]

Config Reg 50

[0, 0]

Config Reg 51

[175, 64]

Config Reg 52

[0, 0]

Config Reg 53

[0, 0]

Config Reg 54

[0, 0]

Config Reg 55

[0, 0]

Config Reg 56

[0, 0]

Config Reg 57

[0, 0]

Config Reg 58

[0, 0]

Config Reg 59

[8, 0]

Config Reg 60

[2, 40]

Config Reg 61

[0, 136]

Config Reg 62

[1, 8]

Config Reg 63

[0, 0]

Config Reg 64

[0, 0]

Config Reg 65

[0, 1]

Config Reg 66

[0, 0]

Config Reg 67

[0, 0]

Config Reg 68

[0, 0]

Config Reg 69

[0, 0]

Config Reg 70

[0, 68]

Config Reg 71

[25, 10]

Config Reg 72

[49, 195]

Config Reg 73

[0, 0]

Config Reg 74

[255, 1]

Config Reg 75

[31, 0]

Config Reg 76

[31, 7]

Config Reg 77

[3, 0]

Config Reg 78

[15, 79]

Config Reg 79

[28, 193]

Config Reg 80

[0, 0]

Config Reg 81

[0, 255]

Config Reg 82

[0, 255]

Config Reg 83

[0, 0]

Config Reg 84

[0, 255]

Config Reg 85

[0, 255]

Config Reg 86

[0, 0]

Config Reg 87

[0, 255]

Config Reg 88

[0, 255]

Config Reg 89

[0, 0]

Config Reg 90

[0, 255]

Config Reg 91

[0, 255]

Config Reg 92

[17, 17]

Config Reg 93

[0, 0]

Config Reg 94

[0, 0]

Config Reg 95

[1, 35]

Config Reg 96

[69, 103]

Config Reg 97

[0, 1]

Config Reg 98

[0, 0]

Config Reg 99

[0, 0]

Config Reg 100

[9, 0]

Config Reg 101

[191, 15]

Config Reg 102

[223, 7]

Config Reg 103

[127, 15]

Config Reg 104

[255, 7]

Config Reg 105

[63, 15]

Config Reg 106

[127, 7]

Config Reg 107

[223, 15]

Config Reg 108

[0, 3]

Config Reg 109

[0, 0]

Config Reg 110

[0, 0]

Config Reg 111

[0, 0]

Config Reg 112

[0, 0]

Config Reg 113

[0, 0]

Config Reg 114

[0, 0]

Config Reg 115

[0, 0]

Config Reg 116

[0, 0]

Config Reg 117

[0, 0]

Config Reg 118

[0, 0]

Config Reg 119

[0, 0]

Config Reg 120

[0, 0]

Config Reg 121

[0, 0]

Config Reg 122

[0, 0]

Config Reg 123

[0, 0]

Config Reg 124

[0, 0]

Config Reg 125

[0, 0]

Config Reg 126

[0, 0]

Config Reg 127

[128, 10]

When looking for errors, I spotted the 8b/10b disparity error. I'm using an FMC120 from Abaco and a ZCU102, the FMC120/ZCU are both known to work (the Abaco demo runs). I'm now building out a system using the Xilinx core.

What could be causing this? Am I looking at the right spot? Does anyone familiar with this part see anything in this table of values that would go, "Yup, it's setting XYZ!"?

Frustrated, but if it was simple it wouldn't be fun. Thanks all!