Hello,

I have ADS5282EVM. I succesfully connected to spartan 6 sp601 via FMC to ADC adapter.

I would like to clock the ADS5282EVM using spartan6 clock resources and not a function generator.

Is this possible?

Any ideas how can i make it work?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello,

I have ADS5282EVM. I succesfully connected to spartan 6 sp601 via FMC to ADC adapter.

I would like to clock the ADS5282EVM using spartan6 clock resources and not a function generator.

Is this possible?

Any ideas how can i make it work?

Hi,

Although this is possible, it is not recommeneded. You'll have to check the amount of jitter that the FPGA clock has. Any jitter on the ADC clock will result in degraded SNR performance, although if your input frequency is relatively low then the jitter will not play as large of a role in the overall SNR performance.

The theoretical max SNR due to jitter is calculated by SNR = -20log(2pi*Fin*Tj) where Tj is calculated as sqrt( Tjclk^2 + Tjapr^2). Tjapr is the aperture jitter of the part and Tjclk is the jitter from the clock source. As you can see, the SNR due to jitter is dependent on the input frequency. At low frequencies, your SNR will be limited by quantization and environmental noise sources rather than jitter.

-Matt Guibord

Lefteris,

also we started posting some application notes and articles to that topic. Here is a recent one explaining the performance impact in a bit more detail.

http://focus.ti.com/lit/an/slyt379/slyt379.pdf

Tommy

Hello,

Thanks for the replies....

Before work around jitter problem i would like to ask if there is an option for digital clocking on ADS5282EVM or should i use DAC to convert FPGA clock to analog signal?

Lefteris,

I'm not sure what you mean by "digital clocking". The recommended solution is to use a clock synthesizer chip, such as the CDCE72010. The FPGA clock reference could be used as the primary reference for the CDCE chip to insure synchronization. You would need an external VCXO for this solution, but the jitter performance would be superior compared to other options such as the FPGA clock output.

Regards,

Matt Guibord

Hello,

What characteristics should have a LVCMOS clock signal from FPGA?

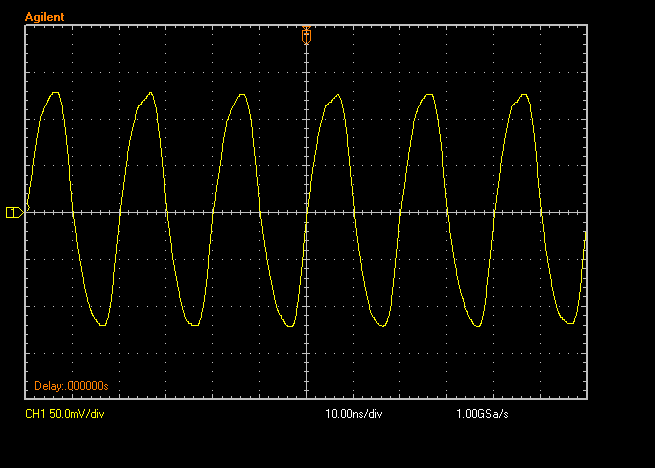

I tried to clock the ADS5282 using a 2.5Vpp 50MHZ clock from the FPGA with no success....

Attached is the output clock in an oscilloscope...

Lefteris,

Check the following jumpers:

JP3: Short 1 and 2

JP4: Short 1 and 2

JP5: Short 1 and 2

Ensure that the chip is set up for a differential clock by writing 0x8001 to register 0x42.

Measure the clock inputs CLKP and CLKN to verify that the clock is reaching the ADC at a sufficient level. Remember that this will be a differential signal, so either use a differential probe to measure the clock peak-to-peak voltage or double the single ended measurement. Make sure the differential Vpp of the clock input is greater than 0.7V.

Regards,

Matt Guibord

Hello Matt,

I measured the voltage level in clock input and find it 0.4Vpp.

How this can happen as before connect it to J26 clock input i measured it and find it 2.5Vpp?

Lefteris

Lefteris,

Is the 0.4Vpp single ended or differential?

Make sure that you don't have any resistance between the FPGA and the clock input that may result in a voltage divider. The clock input has a load impedance of 50 ohms, so any impedance on the line could cause a significant voltage drop. Secondly, make sure the FPGA can drive a 50 ohm load. For a 2.5Vpp signal across a 50 ohm load, the FPGA would need to supply 50mApp. If neither of these are the culprit, then disconnect JP4 and JP5 and measure the voltage across R49 and at pins 1 and 3 of the transformer T9. This will disconnect the source from the ADC and should indicate if its an ADC problem or something else.

Regards,

Matt Guibord

Hello Matt,

0.4Vpp is single-ended measured on JP3(2) pin. The outut from FPGA pin is 2.5Vpp as mentioned above. In JP4 and JP5 i measure 0.2 Vpp differential.

What is between J26 and JP3 that cause this voltage drop? I have no impendance on the line....

Lefteris,

I'm not sure why you would get a voltage drop, unless your clock signal was below the transformers frequency range. I believe you were running it at 50MHz, which is within the 400kHz to 500MHz range of the transformer.

Just to verify, you are measuring 0.2Vpp between pins 1 of JP4 and JP5? If you were measuring 0.2Vpp from pin 1 of JP4 to ground, and 0.2Vpp from pin 1 of JP5 to ground, then this measurement would make since. With a 0.4Vpp input signal, converted to differential, you would expect a 0.2Vpp swing on each leg which would translate to a 0.4Vpp diffferential signal. Check to make sure you measured this correctly.

Secondly, there is a single trace between J26 and JP3 which would not account for the significant loss you're seeing. Did you check to see what kind of load your FPGA's clockout is able to drive? Remember that the clock input on the DAC evm has a 50ohm load which would draw peak currents of 25mA (assuming no DC offset). Can you send me the schematic of what is between the FPGA and the DAC EVM (if anything).

Regards,

Matt Guibord

Hello Matt,

Yes, i measured 0.2 Vpp from pin1 of JP4 to ground and 0.2Vpp from pin 1 of JP5 to ground.

Attached is the schematic of my FPGA device. The ADC J26 clock input is connected with a wire in the 8 pin of GPIO headers. The 2.5 Vpp is measured in the wire just before the J26.

Regards,

Lefteris5265.xtp051_sp601_schematics.pdf

Lefteris,

If I'm looking at the correct point (page 10, header on right side, pin 8) it appears that there is a 200ohm resistor in the path from the FPGA to the ADC board. That resistor is going to form a voltage divider with the 50 ohm input resistance of the ADC board. 2.5 * ( 50 / (200+50) ) = 500mV. If you measure the output of the FPGA before hooking it up to the board, then yes you would see 2.5V, but once the 50ohm load of the ADC is present, this would limit the voltage at the board. I would suggest removing this resistor (R96) and see if that fixes your problem.

Regards,

Matt Guibord

Hello Matt,

You are right..it is a 200 ohm before the pin. i 'll try remove the resistor...

Thank you for the answers..

Regards, Lefteris