HI,

I am using a adc12dj3200 in jmode=3 (dual channel), and using a single channel only at sampling 3200 MHz.

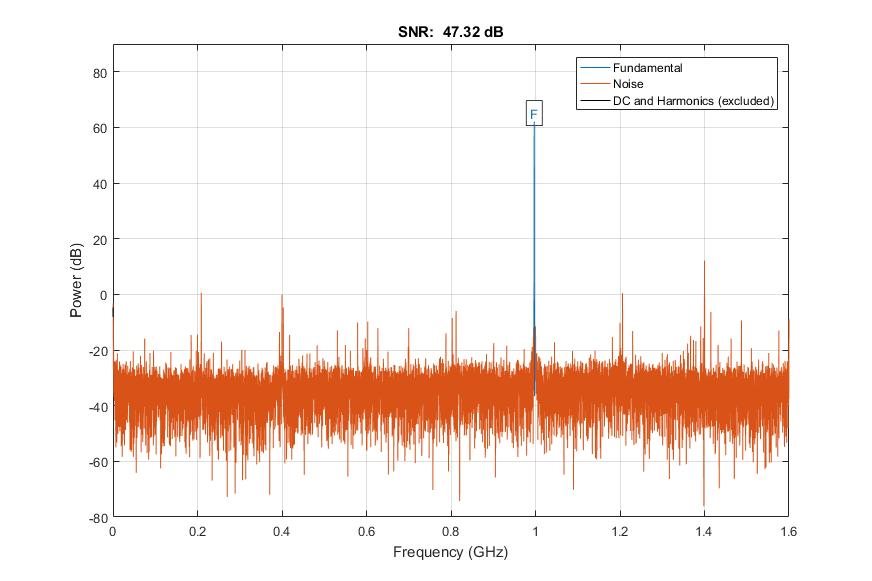

I am trying to improve the SNR via background calibration and offset calibration for continuous operation.

With my best effort I am seeing 47dB SNR. (without offset cal (muting, then background cal enabled I see 30-40dB SNR).

1 - Since I am using one channel , is it possible to dedicate the core C to only service Core A, and not Core B? to

get a better SNR? (would it help?)

Thanks,

Shervin